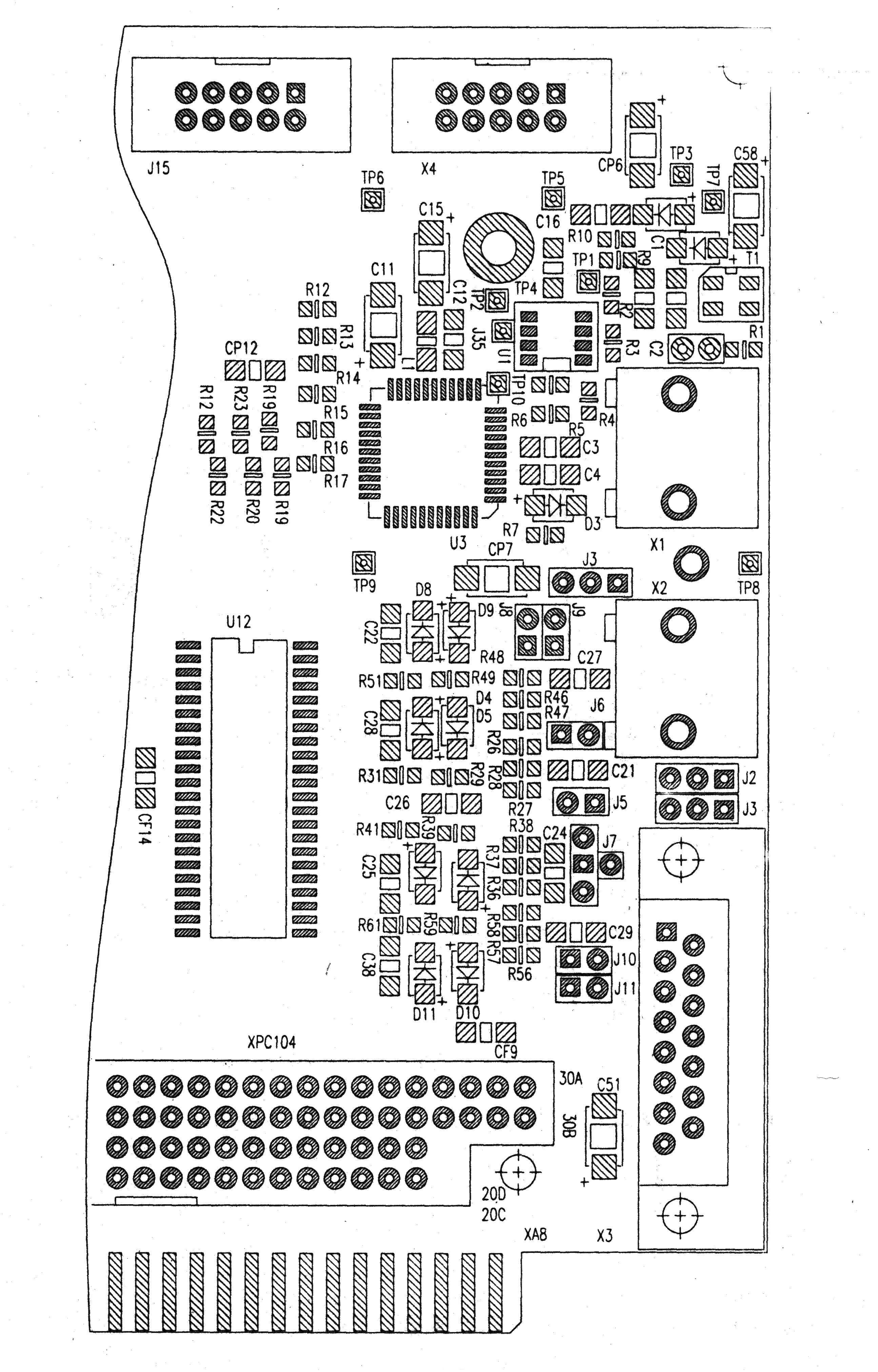

마더보드 표시

컴퓨터 보드 및 주변 장치의 무선 구성 요소

결함이 있거나 오래되었거나 불필요한 컴퓨터 전자 제품에는 저항기, 커패시터, 트랜지스터 등 수많은 요소가 포함되어 있는 경우가 있습니다. 자신의 디자인에 이러한 부품을 사용하고 싶은 유혹이 생길 수 있으며 저항과 커패시터의 경우 모든 것이 명확하지만 트랜지스터와 다이오드의 경우 모든 것이 그렇게 간단하지 않습니다. 대부분의 경우 해당 표시는 2~3개의 기호로 구성되며 이 기호에서 구성 요소를 식별하는 것은 쉬운 작업이 아닙니다. 예, SMD 구성 요소에 대한 지정 테이블이 있습니다. 그러나 일반적으로 구성 날짜는 바로 이러한 구성 요소가 나타나기 오래 전입니다. 따라서 표를 믿는다면 3단자 부분은 다이오드일 수도 있고 2단자 부분은 트랜지스터일 수도 있습니다.

따라서 요소가 흩어져 있는 컴퓨터 근처 패치를 받은 후에는 어떤 부품이 있는지, 어디에 사용할 수 있는지 즉시 확인하는 것이 유용합니다.

최신 요소의 약식 표시는 해당 요소의 데이터시트에서 찾을 수 있습니다. 이는 부품의 브랜드가 약식 마킹 코드에 의해 올바르게 결정된다는 가정을 확인하는 데 유용합니다.

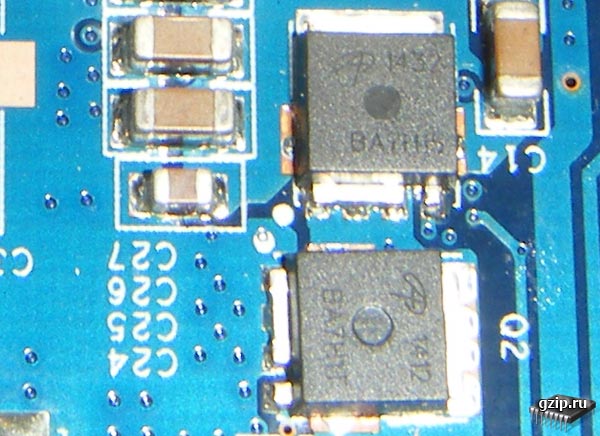

예를 들어 비디오 카드에서 일부 반도체를 디코딩하는 경우를 들 수 있습니다.

1. 표시가 있는 트랜지스터 1412 그리고 1432 . 이는 LFPAK 패키지의 전계 효과 트랜지스터(MOSFET) AOL1412 및 AOL1432입니다.

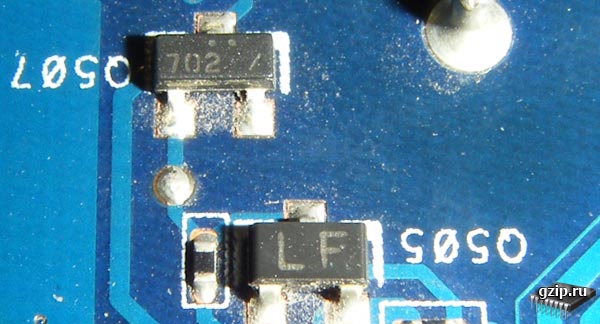

2. 비문이 있는 SOT-23과 유사한 패키지의 3핀 요소 K.J.E., 이 비문에 수직 - 다를 수 있는 두 개의 기호. 이것은 두 개의 BAV99 쇼트키 다이오드의 어셈블리입니다.

3. 표시가 있는 SOT-23 패키지의 3핀 요소 702

- MOSFET 2N7002 입니다. 지정이 있는 SOT-23 패키지의 3단자 요소 LF- 이것 npn 트랜지스터 2SC3052: 0.2A, 50V, 낮은 포화 전압 CE - VCE(sat)=0.3V 최대. (@IC=100mA, IB=10mA).

4. AZ7805D, 5V용 안정 장치 7805.

5. 비문이 적힌 요소 A00B, 아직 확인되지 않았습니다.

6. 표시가 있는 트랜지스터 t06- p-n-p PMBS3906, 100mA 40V, PMBS3904를 보완합니다. VCEsat=최대 −250mV(IC=−10mA; IB=−1mA), 최대 −400mV(IC=−50mA; IB=−5mA;)

7. 표시가 있는 트랜지스터 W04- n-p-n PMBS3904, 100mA 40V, PMBS3906을 보완합니다. VCEsat=최대 200mV(IC=10mA; IB=1mA), 최대 300mV(IC=50mA; IB=5mA;)

8. 커패시터전해. 왼쪽의 검은색은 낮은 ESR(희망적으로)이고 오른쪽은 고분자 전해질입니다. 이 커패시터에 대해 더 자세히 이야기할 가치가 있습니다. 주요 차이점은 전해질이 유전 특성이 높은 합성 폴리머로 대체된다는 것입니다. 초저 ESR 외에도 이러한 커패시터는 기존 전해 커패시터와 달리 건조되지 않습니다. 그들은 이상적입니다

마더보드 표시

자주 발생하는 상황: 올바른 것을 찾기 위해 뉴스레터나 컴퓨터 회사의 가격 목록에서 명확하지 않은 문자와 숫자의 끝없는 열을 살펴보면 발음할 수 없는 이름에 정교한 개발자를 불친절한 단어로 한 번 이상 기억할 것입니다. 그들의 제품. 그리고 전문 간행물에 제안을 게재하는 회사는 제공되는 제품에 대한 다소 자세한 정보를 제공하는 데 신경 쓰지 않는 경우가 많습니다. 나는 영업 사원이 종종 "관리자"와 "컨설턴트"라는 자랑스러운 직함을 지니는 상점에 대해 이야기하는 것이 아닙니다. 그러나 어떤 이유로 무지, 악의적 의도 또는 다른 이유로 그들은 그 ( "찻 주전자")가 항상 필요하지는 않지만 거의 항상 매우 비싼 "찻 주전자"를 고집하십시오. 내가 이 모든 일을 어디로 가고 있는지 이미 이해하셨기를 바랍니다. 맞습니다. "힘들게 번 돈"을 무언가에 버리기로 결정했다면 최소한 무엇을 사고 싶은지에 대한 아이디어가 있어야합니다. 그리고 모두가 알고 있듯이 물체의 이름은 마지막 의미와는 거리가 멀고 때로는 운명을 결정하기도 합니다.

컴퓨터 구성 요소의 명칭을 고려할 때 가장 이해하기 어려운 것은 마더보드의 명칭입니다. 컴퓨터 시장의 다른 어떤 부문도 거의 끝없는 수의 제조업체가 제공하는 수많은 제안을 알지 못합니다. 그리고 많은 가격 목록에서 보드 옵션 수가 두 자릿수 값에 도달하는 경우가 있습니다. 그러나 각 제조 회사에는 순전히 개별 지정 시스템이 있습니다. 아래 자료는 잠재적 구매자가 다양한 회사의 "마더보드" 명칭 집합을 탐색하고 일부 제조업체가 마더보드 명칭에 포함하는 정보를 추출하도록 돕기 위한 시도입니다.

약간-마더보드는 일반적으로 두 개의 문자와 숫자로 식별됩니다. 때로는 하이픈으로 주요 명칭과 분리되어 추가 정보를 전달하는 기호가 있을 수 있습니다.

첫 번째 문자는 칩셋 유형을 결정합니다.

- B-440BX;

- Z-440ZX;

- C-i820;

- S-i815;

- W-i810;

- V - VIA 칩셋;

- K - Athlon 프로세서용 VIA 칩셋;

숫자는 프로세서 유형을 나타냅니다.

- ;

예: VL6은 소켓 370 프로세서 소켓이 있는 VIA Apollo Pro 133 칩셋 기반 마더보드입니다.

Aopen 마더보드는 일반적으로 다음 기호로 식별됩니다.

첫 번째 문자 - 폼 팩터:

- A-ATX;

- M - 마이크로-ATX;

두 번째 문자 - 사용된 프로세서 유형:

- X - Intel에서 제조한 프로세서

- K - AMD에서 제조한 프로세서입니다.

번호 - 프로세서 소켓 유형:

- 3 - 소켓 370;

- 6 - 슬롯 1;

- 7 - 슬롯 A;

다음 문자는 칩셋 유형입니다.

- B - 440BX/ZX(ZX 칩셋에는 추가 인덱스 EZ가 있음);

- Z-440ZX;

- C-i820;

- S-i815;

- W-i810;

- L-440LX;

- P3(P2) - 슬롯 1;

- CU - 소켓 370;

- K7 - 슬롯 A;

- A7 - 소켓 A.

세 번째 문자는 칩셋 유형입니다.

- B-440BX;

- Z-440ZX;

- W-i810;

- S-i815;

- C-i820;

- R - 서버웍스;

- V - 경유;

- M-AMD;

- S - SiS;

- A - 알리.

마지막에는 추가 기능을 표시하기 위해 기호를 사용할 수 있습니다. 예를 들면 다음과 같습니다.

- 4X - VIA Apollo Pro 133A 칩셋;

- 2 (-E) - i815, i820 칩셋의 "E" 수정;

- -1394 - 통합 컨트롤러 IEEE-1394;

- -S - 통합 SCSI 컨트롤러;

- -L - 통합 네트워크 컨트롤러;

- -D - 이중 프로세서 보드;

- -V - 통합 오디오.

표준 ATX 이외의 폼 팩터를 사용하는 마더보드에는 다음과 같은 명칭이 있습니다.

- -B -베이비-AT;

- -M(-RM) - 마이크로-ATX;

- -FX - 플렉스-ATX;

- -N-NLX.

예: CUSL2 - ATX 형식 마더보드, i815 칩셋 기반, 프로세서 소켓 - 소켓 370.

Biostar - 마더보드는 일반적으로 문자 M으로 지정됩니다.

숫자:

- 5 - 5세대 프로세서(Pentium MMX, AMD K6, Cyrix/IBM 6x86 등);

- 6 - 6세대 프로세서(펜티엄 II/III, 셀러론);

-

첫 번째 문자는 칩셋 제조업체입니다.

- T - 인텔;

- V - 경유;

- S - SiS;

- A-알리;

- 남-AMD.

두 번째 문자(Intel 칩셋):

- B-440BX;

- Z-440ZX;

- W-i810;

- C-i820;

- S-i815.

예: M6TSВ는 Pentium II/III, Celeron 프로세서용 Intel 815 칩셋을 기반으로 하는 마더보드입니다.

Chaintech - 마더보드는 CT 기호로 지정됩니다.

첫 번째 숫자 - 프로세서 유형:

- 5 - 5세대 프로세서(Pentium MMX, AMD K6, Cyrix/IBM 6x86 등);

- 6 - 6세대 프로세서(펜티엄 II/III, 셀러론);

- 7 - 7세대 프로세서(AMD K7 Athlon, Duron).

첫 번째 문자 - 칩셋 유형:

- A, V - VIA 칩셋;

- S - SiS 칩셋;

- R - 알리 칩셋;

- B, C, O, W - Intel 칩셋(각각 BX, i820, i815, i810)

두 번째 문자 - 폼 팩터 및 프로세서 소켓 유형:

- J - ATX 보드, 소켓 유형 커넥터;

- I - Micro-ATX 보드, 소켓 유형 커넥터;

- T - ATX 보드, 슬롯형 커넥터;

- S - Micro-ATX 보드, 슬롯형 커넥터;

- F - Flex-ATX 보드, 소켓 유형 커넥터;

- E(G) - Baby-AT 유형 보드, 소켓 7 커넥터.

세 번째 문자는 추가 통합 기능의 존재 여부를 결정합니다.

- M - 표준 보드;

- A - 통합 오디오 시스템;

- V - 통합 비디오 시스템.

예: CT-7AIV2 - 마이크로 ATX 마더보드, 칩셋 - VIA KT133, 프로세서 소켓 - 소켓 A, 통합 그래픽 - RIVA TNT2 M64.

FIC - 마더보드는 일반적으로 지정됩니다.

2개의 문자와 2개의 숫자로 구성된 새로운 마더보드 지정 시스템이 도입되었습니다.

첫 번째 문자는 프로세서 소켓 유형을 나타냅니다.

- A - KT133을 통해;

- S-AMD 750;

- K - Apollo Pro 133/133A를 통해;

- F - 인텔 i810/810E.

두 번째 문자는 칩셋을 식별합니다.

- Z - KT133을 통해;

- D-AMD 750;

- A - Apollo Pro 133/133A를 통해;

- W - 인텔 i810/810E;

- S-인텔 i815;

- B - 인텔 440BX.

대시 뒤의 2자리 숫자는 보드 폼 팩터와 몇 가지 추가 기능을 나타냅니다.

- 1x - ATX;

- 3x - 마이크로 ATX;

- x5 - 내장 비디오 프로세서;

- x7 - 내장 비디오 프로세서 및 네트워크 카드.

예: KW15 - ATX 형식 마더보드, i810E 칩셋 기반, 소켓 370 프로세서 소켓.

Gigabyte - 마더보드는 일반적으로 GA 기호로 지정됩니다.

- 5 - 5세대 프로세서(Pentium MMX, AMD K6, Cyrix/IBM 6x86 등);

- 6 - 6세대 프로세서(펜티엄 II/III, 셀러론);

- 7 - 7세대 프로세서(AMD K7 Athlon, Duron)

첫 번째 문자는 칩셋 유형입니다.

- D - DDR SDRAM 메모리를 지원하는 7세대 프로세서용 칩셋;

- R - DDR SDRAM 메모리를 지원하는 6세대 프로세서용 칩셋;

- B-440BX;

- Z-440ZX;

- C-i820;

- O-i815;

- W-i810;

- V - 경유;

- Z - VIA Apollo KT133(원래 칩셋은 KZ133으로 지정됨)

- 나 - AMD;

- A-알리;

- S - SiS

두 번째 문자는 보드 폼 팩터입니다.

- X-ATX;

- M - 마이크로 ATX;

- F - 플렉스-ATX.

- D - 듀얼 프로세서 보드:

- 7 - 프로세서 소켓 소켓 370;

- E - i810 - i820 칩셋의 "E" 수정;

- M(Z) - 통합 비디오 프로세서

- -1394 - IEEE1394 컨트롤러;

- W - Wide SCSI 컨트롤러 이상.

예: GA-6RXDW - ATX 형식 마더보드, VIA Apollo Pro266 칩셋, 소켓 370 프로세서 소켓 2개, 통합 듀얼 Ultra160 SCSI 컨트롤러 Adaptec 7899.

PC 파트너:

첫 번째 문자는 칩셋 유형을 나타냅니다.

- BX - 440BX/ZX;

- 815 - i815;

- 810E - i810E;

- 학사-i810;

- KT133 - VIA Apollo KT133 등 등등.

- A-ATX;

- M - 마이크로 ATX;

- F - Flex-ATX;

- B - 베이비-AT.

다음 기호는 프로세서 소켓 유형을 나타냅니다.

- S1 - 슬롯 1;

- S3 - 소켓 370;

- S13 - 소켓 370 + 슬롯 1;

- SLA - 슬롯 A;

- SA - 소켓 A;

- S7 - 소켓 7

예: 810EFS3 - Flex ATX 형식 마더보드, i810E 칩셋, 소켓 370 프로세서 소켓.

첫 번째 문자는 폼 팩터입니다.

- A-ATX;

- M - 마이크로 ATX.

두 번째 문자는 칩셋 유형입니다.

- B-440BX;

- C-i820;

- E-i810, i815;

- V - 경유;

- K - KT133을 통해;

- 나 - AMD;

- S - SiS.

첫 번째 문자는 프로세서 소켓 유형입니다.

- 1.2 - 소켓 370/A;

- 6 - 슬롯 1/A

예: AB61 - 440BX 칩셋의 마더보드, 프로세서 소켓 - 슬롯 1.

구형 마더보드에는 다른 명칭이 있습니다.

Soltek - 마더보드는 일반적으로 SL 기호로 지정됩니다.

첫 번째 숫자는 프로세서 유형입니다.

- 5 - 5세대 프로세서(Pentium MMX, AMD K6, Cyrix/IBM 6x86 등);

- 6 - 6세대 프로세서(펜티엄 II/III, 셀러론);

- 7 - 7세대 프로세서(AMD K7 Athlon, Duron)

두 번째 숫자는 프로세서 소켓 유형입니다.

- 1,2 - Baby-AT, 슬롯;

- 3.4 - Baby-AT, 소켓;

- 5.6 - ATX, 소켓;

- 7 - ATX, 슬롯;

- 8 - ATX, 2슬롯.

한두 글자 - 칩셋 유형(마지막 글자가 결정적임):

- V - 경유;

- K-i820;

- M-i815;

- G,H - i810

- B-440BX;

- Z-440ZX;

- S - SiS

예: SL-75KV-X - VIA Apollo KT133 칩셋, 프로세서 소켓 - 소켓 A, 추가로 VD-Tech(음성 진단 기술) 결함에 대한 음성 알림 시스템을 기반으로 하는 ATX 형식 마더보드입니다.

Soyo - 마더보드는 일반적으로 SY로 지정되며 그 뒤에는 다음이 따릅니다.

첫 번째 숫자 - - 프로세서 유형:

- 5 - 5세대 프로세서(Pentium MMX, AMD K6, Cyrix/IBM 6x86 등);

- 6 - 6세대 프로세서(펜티엄 II/III);

- 7 - 셀러론 프로세서(소켓 370), 이중 프로세서 시스템용 보드에는 디지털 제품군 코드 앞에 문자 "D"가 있습니다.

- K7 - 7세대 AMD 프로세서(슬롯 A).

첫 번째(두 번째) 문자 - 세트 자체의 이름을 포함한 칩셋 유형:

- I - Intel(예: IW는 Intel i810, IB - Intel 440BX 등을 의미함)

- 에스시스

- V - 경유;

- A-AMD.

어떤 경우에는 가장 잘 알려진 Intel 논리 세트(예: IB가 아닌 B)의 보드 지정에서 문자 I가 생략될 수 있습니다.

마지막 문자는 폼 팩터입니다.

- M-마이크로-ATX;

- A-ATX;

- B - 베이비 AT.

예: SY-6IWA는 Pentium II/III 프로세서용 i810 칩셋을 기반으로 하는 ATX 형식 마더보드입니다.

SuperGrace - 마더보드는 일반적으로 SG로 지정됩니다.

- APP/APP133/APP133A - Apollo Pro/133/133A 칩셋을 통해;

- 810/810E - 인텔 i810/i810E 칩셋;

- 815 - Intel i815 칩셋;

- 820 - Intel i820 칩셋;

- 440V - Intel 440 BX 칩셋;

- 440Z - 인텔 440 ZX 칩셋;

- MVP3/MVP4 - VIA MVP3/MVP4 칩셋

마더보드 폼 팩터:

- A (ATX) - ATX;

- M(MATX) - 마이크로 ATX;

- B(AT) - 베이비-AT

프로세서 소켓 유형에 대한 정보(일반적으로 슬롯 1에서는 생략됨):

- D - 커넥터 2개(대개 슬롯 1 및 소켓 370)

- 3 - 소켓 370

- 5 - 소켓 7

예: SG-815ATX3 - i815 칩셋 기반 ATX 형식 마더보드, 프로세서 소켓 - 소켓 370.

Supermicro - 마더보드 이름은 일반적으로 Super라는 단어로 시작됩니다.

프로세서 유형은 S2(슬롯 2), P6 또는 PIII(슬롯 1), 370(소켓 370)으로 정의됩니다.

다음 세 글자는 다음을 나타냅니다.

첫 번째 문자는 보드의 프로세서 소켓 수입니다.

- S - 커넥터 1개

- D - 두 개의 커넥터;

- Q - 커넥터 4개

두 번째 문자는 칩셋 유형입니다.

- B-440BX;

- L-440LX;

- W/E - i810/i810E;

- S-i815;

- C-i820;

- M-i840;

- V-VIA.

세 번째 문자는 추가 정보입니다. 예를 들면 다음과 같습니다.

- S - 통합형 Ultra Wide SCSI 컨트롤러;

- U - 통합 Ultra II SCSI 컨트롤러;

예: Super P6SBU - ATX 형식 마더보드, BX 칩셋, 프로세서 소켓 - 슬롯 1, 통합 Ultra II SCSI 컨트롤러.

- K7 - 슬롯 A 프로세서 소켓 지원

- P6 - 슬롯 1 프로세서 소켓 지원

- S3 - 소켓 370 프로세서 소켓 지원

- P5 - 소켓 7 프로세서 소켓 지원

다음 문자 그룹은 칩셋을 나타냅니다.

- B40,BX - 440BX

- 프로 - VIA Apollo Pro 133/133A;

- KX - 아폴로 KX133을 통해;

- M4 - MVP4를 통해;

- 815 - i815

- 81 - i810

보드 폼 팩터는 하이픈으로 구분됩니다.

- A-ATX;

VIA 칩셋 기반 마더보드에는 일반적으로 두 자리 숫자 인덱스가 있지만 문자 지정은 없습니다.

예: MX6B - i440BX 칩셋 기반 마이크로 ATX 마더보드, 프로세서 소켓 - 슬롯 1.

아수스 - 새로운 마더보드 지정 시스템은 다음과 같습니다. 불행히도 회사는 대부분의 다른 제조업체와 마찬가지로 지정 시스템을 정기적으로 변경하는데, 이는 마더보드가 품질 표준인 일반적으로 인정받는 리더에게는 좋지 않습니다.

처음 두 문자는 프로세서 소켓 유형입니다.

M - 마이크로 ATX

예: ATX 형식의 K7KX-A 마더보드, VIA Apollo KX133 칩셋, 슬롯 A 프로세서 소켓.

이 리뷰는 제시된 정보에 대해 완전하고 최종적인 척하지 않습니다. 마더보드에 정기적으로 등장하는 새로운 칩셋, 형식 및 추가 장치는 해당 지정의 새로운 요소에 생명을 불어넣습니다. 지다나 럭키스타 등 많은 회사들은 제품명에 어떤 시스템도 고수하지 않습니다(시스템이 있을 수도 있지만 알아차리기 어렵습니다). 디지털 4자리 인덱스의 유사한 시스템을 사용하는 MicroStar 또는 A-Trend와 같은 심각한 제조업체의 지정에서도 저자는 어떤 패턴도 식별할 수 없었습니다(대부분의 제조업체에서 프로세서 세대를 나타내는 첫 번째 숫자, 계산되지 않습니다). 또한 일반적으로 보드 지정을 위해 특정 시스템을 고수하는 일부 제조업체는 일반 범위에서 특정 모델을 강조하기 위해 회사 자체가 정한 규칙에서 벗어나는 경우가 있습니다. Gygabyte의 GA-BX2000Plus 마더보드가 그 예입니다.

컴퓨터 지원 설계(CAD) 시스템을 갖춘 개인용 컴퓨터의 개발 엔지니어 및 설계자가 등장하면서 인쇄 회로 기판(PCB)의 전자 전자 모듈과 같은 제품의 개발 및 제조에서 노동 생산성이 질적으로 도약했습니다. . 이 경우 전체 설계 프로세스를 하나의 작업장에 집중하는 것이 가능해집니다. 회로, 구조 및 기술 설계에 참여하는 참가자 간의 전통적인 역할 분배에서 벗어나십시오. 이는 경제적 이유로 별도의 설계 및 기술 서비스를 유지하는 것이 수익성이 낮은 직원 수가 적은 회사의 경우 특히 그렇습니다. 이러한 상황에서 REA 모듈 개발을 담당하는 전문가는 다음과 같습니다. 전기 다이어그램건설적인 구현에 앞서 관련 분야의 지식, 특히 PP 기술을 알아야 합니다.

PP 요소 유전체 베이스, 인쇄 도체 및 접촉 패드 패턴 형태의 금속 코팅, 장착 및 고정 구멍입니다.

소프트웨어에 대한 일반 요구 사항.

PP의 유전체 베이스는 색상이 균일하고 구조가 모놀리식이어야 하며 내부 기포 및 공동, 이물질 함유물, 칩, 균열 및 박리가 없어야 합니다. 금속의 단일 포함, 긁힘, 단일 에칭되지 않은 부분 제거로 인한 흔적, 재료 구조의 발현이 허용됩니다. 이는 PCB의 전기적 매개변수를 저하시키지 않으며 전도성 요소 사이의 최소 허용 거리를 줄이지 않습니다. 무늬.

PP의 전도성 패턴 부풀어오름, 벗겨짐, 찢어짐, 도구 자국 및 기술 재료의 잔여물이 없어야 하며 가장자리가 매끄러워야 합니다. 다음이 허용됩니다: 도체의 나머지 폭이 도면에 따라 허용되는 최소값과 일치하는 경우 PP 1dm2당 5점 이하의 개별 국지 매염제; 깊이가 25미크론 이하이고 길이가 최대 6mm인 위험; 요소 사이의 허용 거리를 줄이지 않는 PP 영역의 금속화 잔류물.

내식성을 높이고 납땜성을 향상시키기 위해 전도성 패턴의 표면에 전해 코팅을 적용합니다. 전도성 패턴은 파손, 벗겨짐, 화상 없이 연속적이어야 합니다. 어떤 경우에는 다음이 허용됩니다. 도체 당 2mm2 이하이지만 보드에서는 5개 이하의 코팅되지 않은 영역; 높이가 0.2mm 이하인 국소 성장; 납땜성을 손상시키지 않으면서 코팅의 색상이 어두워지고 고르지 않게 됩니다. 도체 끝 부분에 코팅이 부족합니다. 인쇄된 도체에 중대한 결함이 있는 경우 체적 결함과 함께 복제됩니다(최대 120x180mm 크기 보드의 경우 도체 5개 이하, 크기 120x180mm 이상의 보드의 경우 도체 10개 이하).

장착 및 고정 구멍은 도면 요구 사항에 따라 위치해야 하며 PP 정확도 등급에 따라 결정된 허용 편차가 있어야 합니다. 솔더 조인트의 신뢰성을 향상시키기 위해 내면장착 구멍은 두께가 25미크론 이상인 구리 층으로 덮여 있습니다. 코팅은 연속적이고 내포물이 없는 플라스틱이어야 하며 미세한 결정질 구조를 갖고 유전체 베이스에 단단히 부착되어야 합니다. 이는 1~1.5N의 접점 부하와 3~4회의 리드 재납땜을 통해 3초 동안 250A/mm2의 전류 부하를 외관 변화, 타거나 벗겨짐 없이 견뎌야 합니다. 온도 변화에 주기적으로 노출된 후 금속화된 홀의 전이 저항은 일반적인 기후 조건 하의 저항 값과 20% 이상 차이가 나서는 안 됩니다. 구멍에는 직경이 0.2mm 이하인 뾰족한 비금속 영역이 허용됩니다. 보드에 있는 구멍의 수는 전체 수의 0.3%를 초과해서는 안 됩니다. 허용할 수 없는 손상이 있는 경우 중공 리벳을 사용하여 금속화 구멍을 복원하고 그 수는 전체 구멍 수의 2%를 초과해서는 안 되며 10개를 초과해서는 안 됩니다. PP에. MPP의 외부 층과 내부 층 사이의 임시 비관통 금속화 구멍은 프레싱 공정 중에 수지로 채워야 하며, 이는 가스 함유물이 없어야 하며 접촉 패드로 흐르지 않아야 합니다.

패드는 인쇄된 도체를 장착 구멍의 도금에 연결하는 금속 도금 부분입니다. 해당 영역은 드릴링 중에 파손이 발생하지 않고 너비가 50미크론 이상인 구리 밴드가 남아 있어야 합니다. 접촉 패드의 파손은 허용되지 않습니다. 이는 도체의 전류 운반 용량과 유전체 접착력을 감소시키기 때문입니다. 도체 영역 외부의 개별 접촉 패드(최대 2%)를 부분적으로 분리하고 에폭시 접착제를 사용한 수리가 허용됩니다. 장착 구멍의 접촉 패드는 3~5초 이내에 납땜으로 균일하게 젖어야 하며 유전체 박리, 팽창 및 벗겨짐 없이 최소 3회(MPP-2) 납땜 재납땜을 견뎌야 합니다.

PCB 제조 기술 프로세스는 사용되는 구조 재료의 전기물리적, 기계적 특성을 저하해서는 안 됩니다. 최소 거리가 0.2-0.4 mm인 인접한 두 PP 요소 사이의 절연 저항은 유리 섬유의 경우 낮아서는 안됩니다.

a) 정상적인 기후 조건(온도 25±1°C, 상대 습도 65±15%, 대기압 96-104kPa)에서 10000MOhm;

b) 60±2°C의 온도에 노출(2시간) 후 1000MOhm, 및 ±85±2°C의 온도에 노출(2시간) 후 300MOhm;

c) 4일 숙박 후 20MOhm. 온도 40±2°C, 상대습도 93±3%, 5Mohm(10일 후), 1Mohm(21일 후)인 챔버에서.

절연 저항의 원래 값으로의 복원은 24시간 이내에 이루어져야 합니다.

전도성 패턴 요소에 의한 절연의 전기적 강도는 전압에서 손상되지 않습니다.

정상 조건에서는 700V;

- 40±2C의 온도에서 2일 동안 상대습도 93±3%에 노출된 후 500V;

- 각각 53.6 및 0.67 kPa의 감소된 압력에 노출된 후 350 및 150 V.

MPP 내부 레이어의 경우 지정된 테스트 전압 값이 15% 증가합니다.

생산 과정에서 PP 변형이 발생하여 휘어짐과 뒤틀림이 발생합니다. 변형의 크기는 호일 유전체의 기계적 강도, 호일을 빼낸 후 응력 상태의 특성, 가열 및 냉각 모드의 정확성에 의해 결정됩니다. 두께가 0.8mm 이하인 보드에서는 변형이 제어되지 않으며 두께가 1.5-3mm인 경우 길이 100mm당 변형이 초과해서는 안 됩니다. 유리 섬유의 이중층 보드의 경우 0.8mm, getinax의 경우 0.9mm ; 단층 유리섬유 라미네이트의 경우 0.9mm, getinax 1.5mm. PP가 260~290°C의 높은 온도에 10초 동안 노출되면 전도성 코팅이 파열되거나 유전체 베이스가 벗겨지는 일이 없어야 합니다.

인쇄 회로 기판의 종류. 인쇄된 전도성 층의 수에 따라 인쇄회로기판은 단층, 이중층, 다층으로 구분됩니다. 처음 두 가지 유형은 단면 및 양면이라고도 합니다.

단면 인쇄 회로 기판(SPC) 금속화 없이 또는 장착 구멍을 금속화하여 적층된 프레스 또는 양각 주조 베이스 위에 만들어집니다. 적층 유전체 보드는 설계가 간단하고 제조 비용이 저렴합니다. 인쇄된 도체를 완전히 배선하는 것이 불가능한 경우 장착된 점퍼가 사용됩니다. 가정용 무선 장비, 전원 공급 장치, 통신 장비, 간단한 전자 장비 및 보조 장비의 설치에 사용됩니다. 저비용, 고가공성, 내열성이 릴리프캐스트 PP이며, 한쪽면에 요소가 있습니다. 인쇄 회로 조립, 기타 - 체적 요소(커넥터 하우징, 부품 및 전기 부품 고정용 주변 장치, 방열판 등). 이러한 보드에서는 하나의 기술 주기로 전체 구조가 장착 구멍과 표면 장착 전기 요소의 위치를 위한 특수 홈으로 생산됩니다. 현재 엠보싱PP 기술이 집중적으로 개발되고 있다.

양면 인쇄 회로 기판(DPP) 유전체 또는 금속 베이스의 양쪽에 전도성 패턴이 있고 고밀도 구성 요소 배치 및 라우팅을 제공합니다. 층에서 층으로 도체의 전이는 금속화된 비아를 통해 수행됩니다. 이 보드를 사용하면 양면을 포함하여 표면에 부품을 장착할 수 있고 금속 구멍에 축 리드와 핀 리드가 있는 부품을 장착할 수 있습니다. DPP는 전자 장비 모듈 생산에 사용되는 가장 일반적인 PP 유형으로 측정 장비, 제어 및 자동 조절 시스템에 사용됩니다. 금속 베이스에 인쇄 배선 요소를 배열하면 고전류 장비의 열 제거 문제를 해결할 수 있습니다.

다층 인쇄 회로 기판(MPC) 2개 이상의 층에 전도성 패턴이 있는 절연 재료의 교번 층으로 구성되며, 그 사이에 필요한 연결이 이루어지며, 접착 스페이서로 압착하여 모놀리식 구조로 연결됩니다. 전도성 층 사이의 전기적 연결은 특수 체적 부품, 인쇄 요소 또는 화학적 갈바닉 금속화를 통해 수행됩니다. OPP 및 DPP에 비해 신뢰성과 설치 밀도가 향상되고 기계적 및 기후 영향에 대한 저항성이 있으며 접점 크기와 수가 감소하는 것이 특징입니다. 그러나 제조의 높은 노동 강도, 높은 설계 정확도 및 개별 레이어 조합, 모든 작업에서 신중한 제어의 필요성, 낮은 유지 관리성, 기술 장비의 복잡성 및 높은 비용으로 인해 MPP는 신중한 용도로만 사용할 수 있습니다. 전자 장비의 디자인을 개발했습니다.

REA는 또한 구조적으로 OPP 또는 DPP와 유사하게 설계되었지만 두께가 0.1~0.5mm인 탄성 베이스에 유연한 인쇄 회로 기판(FPC)을 사용합니다. 기판을 제작한 후 진동이나 반복적인 굽힘 현상이 발생하거나, 전자부품을 장착한 후 곡면 형태를 부여해야 하는 경우에 사용됩니다. FPC의 한 유형은 FPC(Flexible Printed Cable)로, 그 위에 인쇄 도체가 배치된 하나 이상의 비전도성 층으로 구성됩니다. GPC의 두께 범위는 0.06~0.3mm입니다. 전자 장비의 구성 요소와 블록을 연결하는 데 사용되며 부피가 작고 원형 묶음 및 케이블보다 가벼우며 압연 소재로 연속 생산이 가능합니다.

PP베이스는 재료의 종류에 따라 다음과 같이 나뉩니다.

유기 유전체(textolite, getinax, Fiberglass)를 기반으로 만들어졌습니다.

세라믹 재료를 기반으로 제작되었습니다.

금속을 기반으로 만들어졌습니다.

레이어 간 연결 유형에 따라 금속 구멍이 있는 PCB, 레이어별 빌드업으로 만들어진 피스톤이 있는 PCB, 개방형 접촉 패드가 있는 PCB가 있습니다.

PCB는 제조방법에 따라 화학적 에칭(Chemical Etching) 방식, 전기화학적 증착(Electrochemical Deposition) 방식, 복합 방식으로 만들어진 보드로 구분된다.

PP는 도체를 도포하는 방법에 따라 유전체 포일을 가공하고 얇은 도전층을 도포한 보드로 구분됩니다. 후자의 방법은 하이브리드 회로 기술을 사용하여 잘 개발되었습니다.

세라믹 기반 MPP가 널리 보급되고 있습니다. 유기 유전체와 비교하여 세라믹은 열 방출을 개선하고 미세 회로의 패키징 밀도를 높일 수 있습니다(특히 마이크로 패키지 사용 시). 세라믹 MPP의 단점은 질량이 크고 최대 선형 치수가 작다는 점입니다(기술에 따라 약 150 x 150mm로 제한됨).

금속 PP는 강철, 알루미늄 및 Invar 시트를 기반으로 만들어집니다. 플레이트는 산화되어 세라믹, 에나멜, 바니시 또는 기타 유전체 층으로 덮여 있습니다. 인쇄된 도체, 필름 저항기, 커패시터 및 인덕터가 상단에 적용된 다음 미세 회로(일반적으로 패키지 해제)가 실장됩니다. 장점 - 상대적으로 저렴한 비용, 무제한의 크기, 높은 열전도율, 높은 소음 내성, 고강도 및 내열성. 단점 - 도체의 높은 비정전 용량과 큰 질량.

인쇄 회로 기판 설계 문제. REA에서 인쇄 회로 기판은 구조 계층의 거의 모든 수준에서 사용됩니다. 0에서 - 하이브리드 회로 및 마이크로 어셈블리의 기초로, 첫 번째 및 후속 수준에서 -에 포함된 모든 요소를 기계적 및 전기적으로 결합하는 기초로 사용됩니다. 전기 같은 개략도 REA 및 그 구성 요소. 인쇄 회로 기판 설계를 개발할 때 다음과 같은 상호 관련된 작업이 해결됩니다.

PP의 디자인 특징. 인쇄된 도체의 폭은 허용되는 폭에 따라 계산되고 선택됩니다. 현재 부하, 전도성 물질의 특성, 온도 환경작동 중. 도체의 가장자리는 매끄러워야 하며, 도체에는 팽창, 벗겨짐, 파손, 식각 자국, 기공, 거친 입자 및 균열이 없어야 합니다. 이러한 결함은 도체의 저항, 전류 밀도, 특성 임피던스 및 속도에 영향을 미치기 때문입니다. 신호 전파.

PCB의 외부 또는 인접한 층에 위치한 전도성 패턴 요소 사이의 거리는 허용되는 작동 전압, 유전 특성, 작동 조건에 따라 달라지며 잡음 내성, 신호 왜곡 및 단락과 관련됩니다.

PP 드로잉 그리드 인쇄된 디자인의 요소를 조정하는 데 필요합니다. 장착 및 전환 구멍은 그리드 교차 노드에 있습니다. 메인 그리드 간격은 양방향으로 0.5mm입니다. 이 피치가 특정 설계의 요구 사항을 충족하지 못하는 경우 0.05mm 피치를 사용할 수 있습니다. 핀 피치가 0.625mm인 미세 회로 및 요소를 사용하는 경우 그리드 피치 0.625mm를 사용할 수 있습니다. 인치 시스템에 따라 핀 사이의 거리가 있는 외국산 미세 회로를 사용하는 경우 2.54mm의 배수인 그리드 피치를 사용할 수 있습니다.

장착 구멍과 전환 구멍(금속화 및 비금속화)의 직경은 0.4 범위에서 선택해야 합니다. 0.5; 0.6; 0.7; 0.8; 0.9; 1.0; 1.1; 1.2; 유; 1.4; 1.5; 1.6; 1.7; 1.8; 2.0; 2.1; 2.2; 2.3; 2.4;2.5; 2.6; 2.7; 2.8; 3.0. 마운팅 홀은 초소형 회로 및 전기 전자 장치를 설치하기 위한 것이며, 비아 홀은 PCB의 레이어 또는 측면 사이의 전기 통신을 위한 것입니다.

PP 크기 , 기술 사양에 특별히 명시되어 있지 않은 한, 설치할 요소의 수, 설치 면적, 설치 피치, 커넥터 설치 면적 등을 고려하여 결정됩니다. PCB 측면의 선형 치수 비율은 다음과 같습니다. 3:1을 넘지 않아야 합니다.

높은 온도와 습도에 노출되면 PP 곡률(베이스의 원통형 또는 구형 곡률)이 나타날 수 있습니다. 길이 100mm에서 PP의 허용 굽힘 값은 OPP 및 DPP의 경우 1.5mm입니다. MPP의 경우 - 2.0mm.

OPP, DPP 및 MPP 외부 레이어에 허용되는 전류 밀도는 20A/mm2입니다. MPP 내부 레이어용 - 15 A/mm2. PP와 GPC의 인접한 층에 위치한 전도성 패턴 요소 사이의 허용 작동 전압은 기본 재료에 따라 다릅니다. 인쇄 회로 기판왼쪽 표에 명시된 값을 초과해서는 안됩니다.

PCB의 외부 레이어에 위치한 전도성 패턴의 요소 사이에 허용되는 작동 전압은 PCB의 기본 재질, 작동 조건에 따라 달라지며 다음 값을 초과해서는 안됩니다(아래 표 참조).

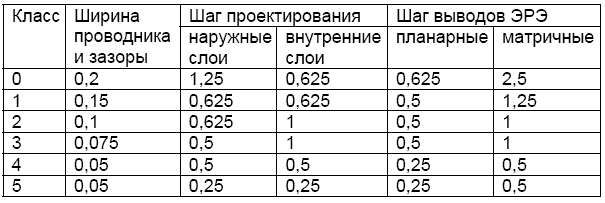

PP 정확도 등급. 국내 표준 GOST 23751-86은 PP의 5가지 정확도(패턴 밀도) 등급을 제공합니다(표 참조). 정확도 등급의 선택은 생산 과정에서 달성된 기술 장비의 수준에 따라 결정됩니다. 설계 문서에는 PP에 필요한 정확도 등급 표시가 포함되어야 합니다.

첫 번째 및 두 번째 정확도 등급의 보드는 제조가 쉽고 저렴하며 생산을 위해 높은 기술 지표를 갖춘 장비가 필요하지 않지만 높은 레이아웃 및 라우팅 밀도로 구별되지 않습니다.

4등급 및 5등급 보드 제조의 경우 특수 고정밀 장비, 특수 재료, 포토마스크 생산용 비수축 필름, 생산 현장의 이상적인 청결이 요구되며 "깨끗한" 영역 생성까지(밀폐형) 구역) 에어컨을 사용하고 안정적인 온도 및 습도 체계를 유지합니다. 기술 모드광화학 및 갈바노화학 공정은 높은 정밀도로 유지되어야 합니다.

3급 보드의 대량 생산은 전문 장비이기는 하지만 일반 장비가 필요하고 재료 및 기술에 대한 요구 사항이 너무 높지 않기 때문에 대부분의 국내 기업이 마스터했습니다.

외국 표준에서는 PP 정확도에 대해 다른 분류를 설정했습니다. 이 분류는 설계 단계 및 부품 접촉 피치와 관련이 있습니다. 표를 보면 인쇄된 패턴의 요소 중 도체의 폭과 간격만 표준화되어 있음을 알 수 있습니다. 정확도 자체에 관해서는 가장 거친 0 등급 보드가 국내 대량 3 등급 보드보다 정확도가 우수한 것으로 나타났습니다. 설계 단계 및 핀 간격에 대한 데이터는 보드의 정확도를 사용된 구성 요소 기반, 특히 MM 패키지 유형과 연관시킵니다.

인쇄 회로 기판의 치수. 일반적으로 PCB 크기는 기능적 및 기술적 두 가지 영역의 요구 사항에 따라 선택됩니다.

건설적인 측면에서 기능적 방향의 요구 사항은 마이크로 회로 패키지의 크기와 수, 전기 회로의 능동 및 수동 연결 설치 유형에 따라 달라지는 배열의 밀도로 표현됩니다. 기술 방향의 요구 사항에 따라 기술 역량 및 공작물 생산 효율성, 포토리소그래피 해상도, 기계적 강도 및 컴퓨터 지원 설계 시스템 기능 측면에서 표준 크기의 제한이 결정됩니다.

PP 크기에 대한 요구 사항은 국내 및 해외 표준에 의해 규제되며, 그 중 가장 일반적인 표준은 실제로 국제 표준이 되었습니다. 국내 표준 GOST 10317-79는 PP 크기에 대해 다음 요구 사항을 설정합니다.

1) 최대 측면 크기는 470mm를 넘지 않습니다.

2) 측면의 치수는 다음의 배수여야 합니다.

측면 길이가 100mm 이하인 2.5mm;

측면 길이가 350mm 이하인 5.0mm;

측면 길이가 350mm를 초과하는 경우 10.0mm;

3) 가로세로 비율은 3:1을 넘지 않아야 합니다.

4) 그리드 피치는 0.5mm, 1.25 또는 2.5mm 여야 합니다.

후자의 요구 사항은 0.5mm보다 작은 피치를 가진 구성 요소가 나타나고 인치 단위의 피치를 가진 외부 구성 요소가 사용되었기 때문에 더 이상 사용되지 않습니다. 또한 CAD ACCEL P-CAD 2000/2001은 미터법 단위로 구성된 경우에도 모든 크기의 내부 인치 표현을 사용하며 데이터를 0.001mm의 정확도로 밀리미터 크기로 출력할 때 반올림됩니다. 현대 CNC 기계 작업체의 위치 정확도는 CAD에서 이러한 절차를 사용하는 것을 방해하지 않습니다.

전반적으로 PCB의 설치 및 연결 치수는 일반적으로 하나 또는 다른 기본 시스템과 조정됩니다. 내하중 구조(BNK). 알려진 BNC 시스템은 많이 있으며, 모두 모든 유형과 크기의 직사각형 모양의 보드를 가정합니다. 예외적이고 기술적으로 정당한 경우에만 직사각형 모양에서 벗어나 기능 장치의 특정 설치 및 작동 조건에 적용할 수 있습니다.

국내 실무에서 널리 사용되는 "유럽" 표준 중에서 국제전기기술위원회(International Electrotechnical Commission)의 두 가지 표준인 IEC 297 표준(TES 297-3)과 소위 메트릭 IEC 917 표준(IEC 917-2- 2) 작성자에 따르면 IEC 297 표준을 대체해야 합니다.

IEC 297 표준은 레벨 2 기본 모듈의 전면 패널 너비를 기준으로 19인치라고 합니다. 표준에서 인쇄 회로 기판의 기하학적 치수는 미터법과 인치 치수가 혼합되어 있습니다. 기본 PCB 크기는 100x100mm입니다. 높이 증가 단위는 1.75″=44.45mm입니다. 이 값은 블록 전면 패널 높이의 배수입니다. 이 다양성의 값은 PP 지정에 포함되지만 이 크기 자체는 보드에 없습니다. 길이(깊이) 증가 단위는 60mm입니다. 전면 패널 너비의 다중도 단위는 0.2″=5.08mm입니다.

REA 모듈의 보드 및 기타 설계 요소에 대한 다양한 표준 크기가 IEC 297 표준을 완전히 준수하는 국내 표준 GOST 28601.3-90이 있습니다. 이 시리즈의 4가지 표준 크기 보드는 여러 통합 표준 설계 UTK를 형성합니다. -2 국내에서는 "Europlata"라고 불립니다. BNK의 다른 모든 구조 요소도 이 보드에 공급됩니다.

PP마킹 필수와 추가로 구분됩니다. 필수 표시에는 GOST 2.201-80("십진수")에 따른 PP 지정 또는 포토마스크의 기존 코드, 생산 날짜 및 버전 번호는 물론 보드 제조업체가 포토마스크에 입력한 기술 표시가 포함됩니다. 추가 표시에는 보드의 일련 번호 또는 보드 배치 지정, 설치 위치 윤곽 지정, 구성 요소의 위치 지정 및 모듈의 설치, 조정 및 작동을 용이하게 하는 기타 정보가 포함됩니다.

일부 표시는 도체와 동시에 에칭으로 만들 수 있지만 이를 위해서는 보드에 여유 공간이 있어야 합니다. CAD를 사용하여 설계를 실행할 때 도체 층에 에칭된 표시는 구성 요소가 연결되지 않은 회로가 되며 CAD는 오류 메시지를 생성합니다. 그러나 이러한 표시는 PCB 도면 번호 또는 코드를 표시하는 데 사용되므로 대량 생산 시 다른 표시가 아직 표시되지 않은 보드에도 화학 처리 작업에서 나오는 보드를 식별할 수 있습니다. 마킹 기호의 높이는 최소 2.5mm여야 합니다.

PCB에 여유 공간이 부족하더라도 오프셋 인쇄 방법(메시 인쇄, 실크스크린 인쇄 등)으로 마킹하는 데 방해가 되지 않습니다. 표시가 납땜 부분에 닿아서는 안 됩니다.

PP 도체 패턴 설계. PCB에 접촉 패드를 설계하는 기술(익숙함)은 친숙함의 토폴로지를 최소화하는 것과 관련하여 주어진 노드 밀도를 보장해야 하는 필요성과 관련됩니다. 동시에 설계는 스위칭 패턴의 최적화를 허용하고, 예를 들어 PCB 층 수와 사용되는 층간 비아 수를 줄이고 제조 중 적합한 제품의 수율을 높여 장치 설계를 단순화해야 합니다. 프로세스.

친숙화 레이아웃 설계는 일반적으로 패드 패턴 설계, 마스킹 패턴 설계, 솔더 페이스트 스텐실 설계라는 세 가지 개별 단계로 구성됩니다.

표면 실장 부품용 PCB에 부과되는 주요 제한은 주요 치수(접촉 패드의 피치, 피치 ")의 달성 가능한 해상도 수준과 관련이 있습니다. 접촉 패드 - 통근선' 및 통근선의 피치. 작은 피치로 솔더 점퍼로 솔더 패드를 서로 연결할 수 있습니다. 점퍼를 최소화하기 위해 패드 자체의 크기를 줄일 수 있지만 안정적인 연결을 형성하려면 패드가 구성 요소 본체 아래에서 특정 최소 거리까지 돌출되어야 합니다. 이 경우, 납땜으로 젖은 표면은 납땜의 메니스커스(또는 필렛)를 형성하기에 충분한 면적을 갖게 됩니다. 조립하는 동안 구성 요소를 고정하는 데 사용되는 접착제가 구성 요소의 접촉 패드에 묻지 않도록 하십시오.

납땜성은 공정 반복성을 보장하는 핵심 설계 측면입니다. 초기 불량 테스트 중 적합한 보드의 수율에 가장 큰 영향을 미치는 것은 납땜 및 세척 공정 중 결함 발생 빈도입니다. 리플로우 솔더링 프로세스 자체에서는 결함이 발생하지 않습니다. 예를 들어 보드 토폴로지의 최적화되지 않은 설계로 인해, 스텐실을 통해 솔더 페이스트를 적용하는 프로세스 중에 결함이 발생할 수 있습니다.

PCB 부품용 패드 설계는 어셈블리의 납땜 기술에 따라 달라집니다. 이런 점에서 웨이브 솔더링과 퓨즈 솔더링은 서로 크게 다릅니다.

웨이브 납땜은 납땜 욕조에 담그는 것을 견딜 수 있는 보드 아래쪽에 장착된 표면 실장 구성 요소에만 적용할 수 있습니다. 표면 부품에 웨이브 납땜을 사용하는 것은 납땜되는 패드를 가리는 부품 하우징의 영향으로 제한됩니다. 섀도우 효과를 제거하려면 예를 들어 솔더 배스를 통과하는 PCB의 이동 방향과 같이 구성 요소의 친숙도에 대한 토폴로지 크기를 늘려야 합니다. 즉, 보드(조립) 레이아웃의 밀도는 사용된 납땜 공정 유형에 따라 달라집니다.

부품 방향은 일부 장치 클래스의 효율적인 웨이브 솔더링에도 마찬가지로 중요합니다. 납땜 중 하우징의 세로 축이 보드의 이동 방향과 평행할 때 최상의 결과가 관찰됩니다. 이 방향은 솔더 브리징을 줄이는 데 도움이 됩니다. 이는 실습에서 알 수 있듯이 보드 이동 방향의 구성 요소 하우징 설치 공간 끝에 추가로 사용되지 않은 패드 쌍을 생성함으로써 촉진됩니다. 이러한 패드는 "납땜 트랩" 역할을 하여 부품 설치 공간의 끝 패드에 납땜이 쌓이는 것을 방지합니다. 간단한 SO 또는 직사각형 하우징은 파도 흐름에 평행하거나 수직으로 배향될 수 있습니다. 미터링된 솔더를 사용한 리플로우 솔더링의 경우, 증가된 패킹 밀도에 따라 부품 위치 지정 및 솔더 페이스트 적용의 정확성이 높아져야 합니다. 용융된 솔더에서 부품이 미끄러지는 효과를 고려할 필요가 있습니다. 이 효과는 액체 솔더의 표면 장력(리플로우 중)의 결과로, 부품을 솔더 패드 중앙으로 끌어당기는 경향이 있으며, 이로 인해 일반적으로 부품 위치 정확도가 향상되어야 합니다.

같은 이유로 특히 칩 부품의 경우 접촉 패드의 모양과 크기가 동일한 것이 중요합니다. 그렇지 않으면 각 접촉 패드의 표면 장력 불균형으로 인해 구성 요소가 설치된 위치에서 이동하게 됩니다. 패드의 길이가 너비보다 훨씬 길면 구성 요소가 패드 중 하나만 움직여서 점유할 수 있어 개방 회로가 됩니다. 패드가 너무 넓으면 구성 요소가 필요한 방향을 쉽게 잃을 수 있습니다. 칩 부품용 패드가 서로 연결될 때 발생할 수 있는 특정 문제도 있습니다. 대형 패드가 단일 토폴로지 요소로 설계되면 리플로우 솔더링 중에 솔더의 더 큰 표면 장력으로 인해 각 구성 요소가 이 패드의 중심으로 끌립니다. 하나의 큰 패드 대신 좁은 스위칭 경로로 연결된 두 개의 작은 패드를 설계하는 것이 더 편리하며, 이는 축적된 솔더의 양을 제한합니다.

더 높은 스위칭 전류가 필요한 경우 단일 트랙의 폭을 늘리는 것보다 트랙 수를 늘리는 것이 좋습니다. 왜냐하면 넓은 스위칭 트랙은 부품 아래에 납땜이 쌓이고 부품이 움직일 가능성이 높기 때문입니다. 구성 요소 아래의 라우팅 전환이 여전히 필요한 경우 하나의 넓은 트레이스를 더 작은 너비의 여러 병렬 트레이스로 나누어야 합니다. 두 개의 병렬 칩 구성 요소가 서로 매우 가까이 위치하는 경우에도 바람직하지 않은 슬라이딩 효과가 발생할 수 있습니다. 납땜 공정 중에 슬라이딩 구성 요소가 실제로 인접한 구성 요소 본체 아래의 납땜과 접촉할 수 있습니다. 최소 0.635mm 또는 1.27mm의 간격이 있으면 이러한 미끄러짐 가능성이 줄어듭니다.

좁거나 테이퍼진 스위칭 트랙을 사용하여 큰 접촉 패드 영역을 서로 연결하면 실용적인 좋은 결과를 얻을 수 있습니다. 이는 납땜이 부족할 수 있는 비아에 연결된 패드에 적용됩니다.

PP의 전기적 매개변수 계산. 인쇄된 도체는 충분히 통과합니다. 가까운 거리서로 다르며 비교적 작은 선형 단면 치수를 갖습니다. 전자 전자 장치의 속도가 증가함에 따라 도체의 매개변수와 이들 사이의 고주파 연결을 고려하는 문제가 점점 더 중요해지고 있습니다.

도체 저항은 다음과 같이 주어진다.

여기서: - 도체의 특정 체적 전기 저항; l은 도체의 길이입니다. b - 도체 폭; d는 도체의 두께입니다.

의 값은 다양한 방법으로 만들어진 도체에 따라 다릅니다. 따라서 전기화학적 증착으로 얻은 구리 전도체의 경우 는 0.02-0.03μOhm/m이고 화학적 에칭으로 얻은 구리 전도체의 경우 는 약 0.0175μOhm/m입니다.

도체의 직류. 인쇄된 도체의 전류량은 우선 특정 재료 에 허용되는 최대 전류 밀도 제한에 따라 결정됩니다. 전기화학적 증착으로 얻은 구리 전도체의 경우 는 약 20A/mm2이고 호일의 화학적 에칭으로 얻은 전도체의 경우 약 30A/mm2입니다. 이를 바탕으로 인쇄 도체의 허용 전류는 다음과 같이 결정됩니다.

너비는 다음 조건을 충족해야 합니다.

b 103 I/(d).

인쇄된 도체의 전압 강하는 다음과 같이 정의됩니다.

유 = .

인쇄된 도체의 교류. 직류와 달리 인쇄된 도체의 교류 분포는 고르지 않습니다. 이는 고주파 교류가 도체를 통해 흐를 때 발생하는 표면 효과가 있기 때문입니다.

이 경우 도체 내부에 자기장이 형성되어 주 도체와 상호 작용하는 유도 전류가 나타납니다. 결과적으로 전류는 도체 단면 전체에 재분배되고 결과적으로 단면 주변 영역의 밀도가 증가하고 중심에 가까워질수록 감소합니다. 고주파수에서는 도체 내부 층의 전류가 거의 0으로 감소합니다.

컨테이너. 보드의 같은 면에 위치한 동일한 폭 b(mm)의 두 평행 인쇄 도체 사이의 정전 용량(pf)은 다음과 같이 정의됩니다.

C = 0.12 l/(lg),

여기서: l은 도체가 평행한 부분의 길이, mm입니다. - 매체의 유전 상수; a는 평행 도체 사이의 거리입니다.

유전체 두께가 a(mm)인 인쇄 회로 기판의 양면에 위치한 폭 b(mm)의 두 평행 도체 사이의 정전 용량(pf)은 다음과 같이 정의됩니다.

C = 0.008842 l b/a .

주어진 표현식을 사용하면 (20-30)%의 정확도로 인쇄된 도체의 정전 용량(pf)을 추정할 수 있습니다.

고주파수에서는 인쇄 도체의 인덕턴스와 상호 인덕턴스를 평가하는 것이 필요합니다.

인쇄 회로 기판의 제어를 테스트합니다. 제품의 제조 과정 및 이후 단계의 테스트 관리와 관련된 대부분의 문제 수명주기, 장치 설계 단계에서 충분한 주의를 기울이면 해결 가능합니다.

표면 실장 기술에는 정밀한 기술 공정이 필요합니다. 제품 수리가 기존 기술의 경우보다 훨씬 더 어렵고 비용이 많이 들기 때문입니다. 이는 고품질의 조립과 다양한 기술변화에 따른 결함의 종류와 원인을 인식하여 신속한 결함 수정을 전제로 합니다. 결함 분석에는 일반적으로 기능 테스트 시스템에서 생성된 품질 관리 결과의 통계 처리가 포함됩니다. 예비 테스트 결과를 기준으로 적합한 보드의 수율이 90% 이상이라고 하더라도 이러한 제품의 작동 신뢰성을 보장하기 위해 회로 내 제어 가능성을 제공하는 것은 여전히 필요합니다.

경제적 고려 사항을 바탕으로 예비 테스트는 기능적이어야 하며 이후의 회로 내 테스트는 선택적으로 수행되어야 하며 결함이 있는 보드의 결함 분석을 포함해야 합니다. 회로 내 모니터링은 작은 역할을 할 것으로 예상되지만, 다음을 허용하는 회로 내 모니터링이기 때문에 여전히 프로세스의 필수적인 부분으로 남아 있습니다. 피드백"제품 - 기술적 과정».

안에 복잡한 시스템테스트(테스트) 현장은 물론 설치 밀도를 낮추고 테스트 장비 및 비용도 증가시킵니다. 소프트웨어제어 프로세스. 선택된 테스트 장소에서는 다음을 사용하여 장치의 기능적 능력을 평가하기 위해 충분한 전기물리적 매개변수 세트를 제어할 수 있어야 합니다. 최소 수량플랫폼. 설치 밀도를 줄이지 않는 테스트 사이트를 성공적으로 선택하면 테스트 비용을 최대 40%까지 줄일 수 있습니다.

테스트 제어 설계에 대한 주요 권장 사항은 다음과 같습니다. 테스트 장치의 프로브 접촉은 부품 리드가 아닌 테스트 패드 또는 패드를 통한 중간층으로만 이루어져야 합니다. 보드의 양쪽에서 제어할 수는 없습니다. 보드의 필요한 표면에 테스트 포인트를 출력해야 하는 경우 층간 비아를 사용해야 합니다. 보드 주변 영역은 비어 있어야 합니다. 테스트 장비를 보드에 안정적으로 고정하려면 너비가 3mm 이상인 자유 스트립이면 충분합니다. 프로브 측정은 보드의 한 영역에 집중되어서는 안 됩니다. 보드는 프로브의 영향으로 테스트 중에 변형될 수 있기 때문입니다. 현대에서는 두 프로브 사이의 최소 거리가 1.27mm로 간주되며, 이는 테스트 사이트의 토폴로지를 설계할 때 고려해야 합니다. 더 짧은 거리를 실현할 수 있지만 테스트 장비에 상당한 추가 비용이 발생합니다.

프로빙 측 보드에 설치된 구성요소의 높이는 6.35mm를 초과해서는 안 됩니다. 테스트 패드 배치 공차는 보드의 가이드 기술 구멍을 기준으로 ±0.05mm를 초과해서는 안 됩니다. 보드의 기술 구멍 직경에 대한 공차는 0¼0.0762mm입니다.

인쇄 회로 기판 설계 자동화. 현대 회로의 복잡성이 높기 때문에 인쇄 회로 기판의 구성 요소 배치, 라우팅, 열 조건 계산 및 전자기 상호 작용 작업을 자동화해야 합니다.

본질적으로 배치 및 라우팅 문제는 무차별 대입(전체 또는 부분)으로 귀결됩니다. 가능한 옵션연결할 요소를 배치하고 최적의 요소를 찾는 것입니다. 최적성 기준은 보드에 배치된 모든 인쇄 도체 길이의 최소 합(또는 더 복잡한 목적 함수)입니다.

일반적으로 배치 문제는 표준 설계의 설치 공간에서 특정 기준, 요소의 위치 및 요소 간의 연결의 최적을 결정하는 것으로 구성됩니다. 이 경우 명시된 설계 및 기술적 한계를 만족해야 한다. 이 공식에서 배치 문제는 정수 프로그래밍으로 공식화될 수 있지만 크기가 크기 때문에 실제 구현이 비현실적입니다. 배치 문제는 일반적으로 구조 요소 배치와 요소 간의 연결 추적이라는 두 가지로 나뉩니다. 이 접근 방식을 사용하면 배치 작업이 표준 설계의 장착 영역에서 요소 및 외부 접점의 최적 위치를 찾는 것으로 축소됩니다. 많은 알고리즘에서 요소 배치는 외부 핀과의 연결을 고려하지 않고 수행되므로 외부 핀과 연결된 요소는 해당 요소로부터 상당한 거리에 위치할 수 있으며 이로 인해 후속 연결 추적이 복잡해집니다. 배치 작업의 초기 데이터: 요소 연결 다이어그램

com, 미터법 매개변수 및 설치 공간의 토폴로지 속성. 하위 장치부터 시작하는 일반적인 컴퓨터 설계는 규칙적인 장착 공간이 특징입니다. 그러면 배치 문제는 다음과 같이 공식화될 수 있다. 구조 요소 세트 E=(ei / i=1, N)와 이를 연결하는 체인 세트 Q=(qk /

k=1, K). 설치 공간은 요소 T=(tj / j=1, M) 및 M ≥ N을 설치하기 위한 고정 위치 세트로 정의됩니다. 세트 E를 세트 T로 매핑하는 방법을 찾습니다. 목적 함수 F가 달성됩니다. 배치의 주요 목표는 최고의 조건추적을 위해. 기존의 배치 문제와 라우팅 문제의 분리로 인해 라우팅 요구 사항을 충분히 만족시킬 수 있는 배치 문제에 대한 최적화 기준을 설정하는 것이 어렵습니다. 안에

현재 다음 기준이 사용됩니다: 모든 연결의 최소 총 길이 또는 가장 긴 연결 길이; 모든 구성에 대한 최소 결합 교차 수; 가능한 가장 간단한 구성으로 최대 회로 수; 서로 가장 많은 수의 연결을 갖는 모듈의 가능한 가장 가까운 배열입니다. 지정된 기준은 배치의 주요 문제를 해결하는 데 질적으로만 기여합니다. 가장 일반적인 기준은 연결의 최소 총 길이입니다. 최적화는 연결 길이와 교차점 수를 간접적으로 최소화하고 신호 왜곡을 줄이기 때문입니다.

M 위치에 설치할 수 있는 N 요소의 경우 배치 세트 A=(al / l=1, L), 해당 번호⎧M!/(M − N)! M > N의 경우 L=⎪ ⎨⎪ M!⎩ M = N의 경우.

이에 대해 검색을 통해 최적의 옵션 N=15...20에서도 철저한 검색을 통한 배치는 부적절합니다. 다음에서는 M=N이라고 가정하겠습니다. 요소 개수가 위치 개수보다 적으면 M~N개의 더미 요소를 입력할 수 있습니다. 배치 알고리즘은 주요 그룹으로 요약될 수 있습니다: 배치 문제의 모델인 수학적 프로그래밍 문제를 해결하기 위한 알고리즘; 순차 알고리즘; 반복 알고리즘; 연속-이산 최적화 방법을 사용하는 알고리즘.

연결의 최소 총 길이 기준을 사용하여 배치 문제를 2차 할당 문제로 공식화하는 것을 고려해 보겠습니다. 수학적 모델의 다이어그램으로 우리는 가중치가 부여된 무방향 다중 그래프를 사용할 것입니다. 여기서는 체계의 요소가 정점과 연관되어 있고 각 체인은 완전한 하위 그래프로 표시됩니다. 회로 요소의 연결성은 연결 행렬 R에 의해 제공됩니다. 이 요소 ri,j는 정점 x i ← e i 및 x ←e의 가중치 연결성을 반영합니다. j j Q i, j r = ∑ pq , i, j q=1 여기서 Q는 요소 ei와 ej를 동시에 포함하는 회로의 수입니다. i, j p q = 1/(ρ q − 1) – 무게 q 번째 연결; ρq - 연결된 요소 수 q번째 체인. 연결은 구조 요소의 기하학적 중심에서 시작되고 미터법은 직교하며 수평 및 수직으로 인접한 위치 사이의 거리는 동일하다고 가정합니다. 그러면 설치 공간의 수학적 모델은 격자 그래프 Gr이 되며, 요소의 설치 위치 사이의 거리는 그래프 Dr의 거리 행렬에 의해 결정됩니다. 외부 결론은 요소 e0과 유사합니다. 세트 E의 요소와의 연결은 가중 연결 열의 벡터에 의해 고려됩니다. H=(hi/ I=1, N). 외부 핀의 장착 영역은 일반적으로 표준 설계의 주변에 고정됩니다. 접촉 패드의 위치가 지정됩니다. 전원 및 접지 핀을 제외한 접촉 패드는 변하지 않습니다. 따라서 소자 ei에서 외부단자까지의 거리는 이 소자가 설치된 수직(수평)열에서 접점군까지의 거리로 대략적으로 결정될 수 있다. 일부 배치의 경우 연결의 총 가중치 길이

1N N N

L(a) = ∑ ∑ r d + ∑ h m ,

2 i=1 j=1 i, j i, j i=1 i i

여기서 di,j는 행렬 Dr의 요소이며 구조 요소 ei와 ej의 설치 위치 사이의 거리를 결정합니다. mi - 요소 ei가 위치한 세로 행의 번호입니다.

이제 작업은 배치 집합 A에서 L(a)를 최소화하는 것입니다. 이것은 2차 할당 문제의 변형 중 하나이며, 정확한 해는 예를 들어 분기 및 경계 방법으로 찾을 수 있습니다. 이 방법을 구현하는 알고리즘은 N=15...20에서 실제로 사용될 수 있습니다.

순차적 배치 알고리즘

대부분의 순차 연결 배치 알고리즘의 결정적인 규칙은 가장 많이 연결된 요소가 가능한 한 서로 가깝게 배치되어야 한다는 가정에 기초합니다. 알고리즘의 각 단계에서 특정 추정에 따라 다음 요소와 설치 위치가 선택됩니다. 요소와 위치의 선택은 개별적으로(다양한 추정에 따라) 또는 동시에 수행될 수 있습니다. 개별 선택 원칙을 구현하는 알고리즘은 더 간단합니다. 일부 요소의 위치는 회로 요구 사항에 따라 개발자가 미리 지정할 수 있습니다. 예를 들어 팬아웃 비율이 높은 강력한 요소는 첫 번째 행에 배치해야 합니다.

서브유닛 보드의 출력 접점에서. 고정 요소가 없는 경우 초기 요소 선택 규칙과 설치 위치를 지정해야 합니다. 예를 들어, 중앙 위치 또는 요소의 접촉 그룹에 가장 가까운 위치 행에 최대 연결 수를 가진 요소를 설치하여 초기 배치를 얻을 수 있습니다.

그것과의 최대 연결. 요소 선택과 설치 위치를 분리하는 원리를 사용하는 알고리즘을 고려해 보겠습니다. 요소들의 연결 정도를 평가하여 다음 배치할 요소를 결정하고, 위치 품질 평가를 바탕으로 설치 위치를 결정합니다. 배치할 요소를 선택하기 위해 연결 정도에 대한 다양한 추정이 사용됩니다. 그 중 일부를 살펴보겠습니다. 해보자 k번째 단계알고리즘은 Ek = E 요소를 배치했습니다. 즉, 일부 부분 배치가 있습니다. 요소 E와 설치 위치 T의 집합은 각각 배치된 요소와 점유 위치 Ek, Tk, 그리고 배치되지 않은 요소와 자유 위치 Ek, Tk의 분리된 하위 집합에 속합니다. 알고리즘의 (k+1) 단계에서 요소를 선택하는 주요 결정 규칙은 최대값입니다: 이전에 배치된 요소와의 연결성, 배치된 모든 요소와의 전체 연결성, 배치된 요소와 배치되지 않은 요소와의 연결 차이(연결성 지표 평가) 아래에서 논의하겠습니다).

다음 요소를 설치하기 위한 위치 선택은 배치 기준을 최소화해야 합니다. 연결의 최소 총 길이 기준을 사용할 때 위치 품질에 대한 가장 간단한 평가는 첫 번째 요소 할당 가격의 일부입니다. j번째 위치, 접촉 그룹을 포함하여 이미 배치된 요소와의 연결 전체 길이를 반영합니다. 알고리즘 요소(EA)의 개발 및 구현은 현대 과학 기술 혁명의 주요 지표 중 하나입니다. 전자 장치 제작 분야의 발전은 장치의 신뢰성, 효율성, 품질 및 효율성을 높이고 회로, 설계 및 기술을 개선함으로써 결정됩니다. EA를 만드는 과정은 일반적으로 회로 설계, 설계, 기술의 세 가지 주요 설계 단계로 나뉩니다. 첫 번째 단계에서는 미래 EA의 아키텍처가 개발됩니다. EA의 주요 아이디어의 구체화는 설계 및 생산 기술 단계에서 수행됩니다. 실습을 통해 전자 회로를 마이크로 전자 구조로 변환할 수 있는 가능성이 보장되고 과학, 기술 및 생산의 현대적 요구 사항을 충족하는 실행 가능한 제품이 탄생할 수 있음이 나타났습니다. EA를 만드는 과정에서 수학적 논리, 디자인 및 기술 개발 문제는 밀접하게 얽혀 있습니다. 설계 및 기술적 요소를 고려하지 않고 EA 논리를 조금만 변경해도 주요 특성이 저하됩니다. 확대 기능성 EA의 복잡성으로 인해 과학자와 엔지니어는 새로운 설계 원리와 기술을 모색하고 현대 컴퓨터 기술의 사용을 기반으로 설계 방법을 근본적으로 바꿔야 하는 필요성에 직면하게 되었습니다. 일반적으로 개별 장치와 마찬가지로 EA 회로 설계를 자동화하는 프로세스는 시스템 엔지니어링(시스템 및 구조 설계 포함)의 세 단계로 구성됩니다. 회로 엔지니어링(모델링, 논리적 설계, 진단 테스트의 제어 및 구성); 디자인 (기술 및 기술 디자인). 시스템 설계는 시스템 분석의 아이디어와 방법을 사용합니다. 수많은 요소를 바탕으로 EA 개발을 위한 기술 사양에 대한 포괄적인 분석이 수행되고 구성 방법론과 컴퓨팅 프로세스 구현 방법에 관한 결정이 내려집니다. 구조 설계 중에 EA의 일반적인 구조 다이어그램과 개별 작업을 수행하기 위한 알고리즘이 개발됩니다. 구조를 선택하려면 제조 가능성, 신뢰성, 동종 및 준동종 통합 장치의 폭넓은 사용 가능성에 대한 요구 사항을 고려해야 합니다. 설계의 시스템 엔지니어링 단계는 엔지니어의 창의적인 능력이 사용되는 비공식 프로세스입니다. 전자 컴퓨터는 개발자가 내린 결정에 대한 옵션을 검토하고 최적의 옵션을 선택합니다. 이 단계에서는 블록 다이어그램을 자동으로 획득하여 원래 작업에 따라 계산 프로세스의 변형을 생성하기 위해 특수 언어와 형식적 방법이 사용됩니다. 회로 설계에서는 컴퓨터의 논리 및 컴퓨팅 기능이 널리 사용됩니다. EA의 논리적 설계의 목표는 구조 설계의 결과로 선택된 노드의 자동 또는 자동화된 형식화된 추상 및 구조적 합성으로, 최종 결과에 대한 원래 작업의 동등성을 검증하는 것입니다. 이론적으로 여기에는 상당한 성과가 있습니다. 제어 및 특수 유형의 작동 장치가 자동으로 합성됩니다. 실제로 회로의 논리 설계를 자동화하려면 많은 문제의 해결이 필요합니다. 여기에는 초기 작업을 설명하기 위한 효과적인 언어 개발, 구조 설계 언어, 장치의 공식 모델 구성을 위한 알고리즘 등이 포함됩니다.

논리 설계에서 가장 중요한 최적화 기준은 논리 노드 유형 수 최소화, 논리 블록의 최대 균일성 달성, 회로의 효과적인 모델링 및 진단 가능성, 설계 및 기술 설계 요구 사항의 최대 고려입니다. 모델링 작업은 논리 신호에 대한 상태 맵 구성, 입력 신호 전달 중 타이밍 관계 확인, 주어진 부울 함수 시스템 준수 여부에 대한 기능 다이어그램 분석입니다. 물리적 및 수학적 모델링이 있습니다. EA 회로의 경우 복잡한 집적 회로를 사용하면 물리적 모델링 가능성이 배제되므로 수학적 모델링이 더 중요합니다. 모델링 하위 단계의 개발은 제어 및 진단입니다. 동시에 하드웨어 제어 회로를 구성하는 방법론을 결정하고 테스트 서비스 시스템을 개발하며 필요한 정도와 이중화 수준을 결정하여 최소한의 것을 선택합니다.

1 자동 설치를 위한 인쇄 회로 기판을 준비하는 일반적인 기술 프로세스.

자동 설치를 위해 인쇄 회로 기판을 준비하는 과정은 여러 단계로 나눌 수 있습니다.

- 표면 실장 부품에 대한 요구 사항을 준수하는지 인쇄 회로 기판을 확인합니다.

- 레퍼런스 마크 설치

- 기술을 고려한 기술 블랭크(보드 패널) 생성

장착 장비의 특성, 주문할 보드 수, 제조 기능 및 스텐실 비용 등

- 패널에 "기술 영역" 배치

자동 설치를 위한 인쇄 회로 기판을 준비하는 프로세스는 일반적으로 인쇄 회로 기판 설계 부서에서 수행됩니다. 필요한 경우 패널의 보드 수와 유형은 고객과 합의됩니다.

고객이 제공한 파일에는 단일 보드가 포함되어 있는 것이 바람직합니다.

2 의도된 인쇄 회로 기판 설계 요구 사항 SMT 구성 요소의 자동 설치를 위한 것입니다.

2.1 표면에 부품 및 인쇄 도체 배치

프린트 배선판:

2.1.1 모든 표면 실장 부품을 보드 한쪽에 배치하는 것이 좋습니다. 이 조건이 충족되지 않으면 구성 요소를 "가벼운" 구성 요소와 "무거운" 구성 요소로 나누어 보드의 서로 다른 면에 배치해야 합니다. 예를 들어, 한쪽에는 수동 부품을 배치하고 다른 쪽에 마이크로 회로를 배치합니다.

2.1.2 패드의 치수는 주어진 프레임 크기에 권장되는 치수와 일치해야 합니다(패드의 치수에 대한 정보는 구성 요소에 대한 기술 문서 또는 IPC-782 표준에서 찾을 수 있습니다).

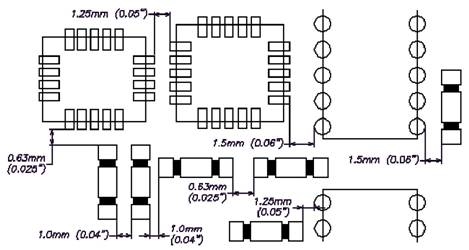

2.1.3 구성 요소 사이의 간격은 그림 1에 표시된 간격보다 작아서는 안 됩니다. 1.

쌀. 1. 부품 간 최소 간격

계약 제조 부서와의 합의에 따라 구성품 간 최소 거리 0.3mm가 허용됩니다.

2.1.4 구성 요소는 기술 필드(스트립)가 있는 경우 공작물 가장자리에서 2mm 이상, 기술 필드(스트립)가 없는 경우 4mm 이상 떨어져 있어야 합니다.

2.1.5 보드의 구성 요소 방향은 근본적으로 중요하지 않습니다.

2.1.6 극성 구성 요소의 방향을 동일한 방식으로 지정하는 것이 좋습니다.

2.1.7 최대 구성 요소 수는 동일한 프레임 크기를 갖는 것이 바람직합니다. 예: 저항기 및 커패시터 - 0805. 이러한 방식으로 구성 요소를 선택하면 설치자가 최대 생산성을 달성할 수 있습니다.

2.1.8 구성요소의 최대 높이는 15mm를 초과해서는 안 됩니다.

2.1.9 리드 피치가 0.5mm 이하인 구성 요소의 경우 가능하면 로컬 참조 표시를 배치할 수 있는 공간(구성 요소의 대각선을 따라 또는 중앙에)을 남겨 두십시오.

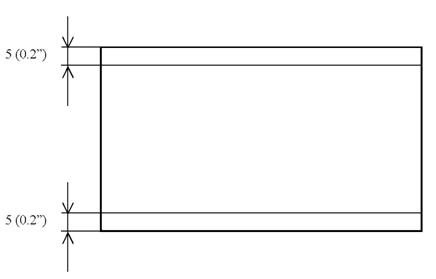

2.1.10 보드 블랭크의 변형은 그림 1에 표시된 값을 초과해서는 안됩니다. 2.

쌀. 2. 보드 블랭크의 허용 변형

2.1.11 보드 제작 및 설치 시 오븐에서 가열 시 보드 변형을 방지하기 위해 외층 및 내층(다층 보드의 경우)의 다각형은 보드 표면에 고르게 배치되고 도체 그리드 형태로 만들어져야 합니다. .

2.1.12 구성 요소 아래에 있는 도체와 비아는 보호 마스크로 덮어야 합니다.

2.1.13 BGA 패키지 아래에 있는 비아 홀은 보호 마스크로 덮어야 합니다.

2.1.14 비금속 구멍의 가장자리에서 접촉 패드 또는 도체까지의 거리는 최소 0.5mm가 되어야 합니다.

2.2 SMT 패드에 도체 연결.

납땜 중 접촉 패드의 열 흐름을 줄이려면("차가운" 납땜의 모양을 제거하기 위해) 다음이 필요합니다.

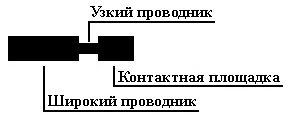

2.2.1 그림 1과 같이 접촉 패드와 넓은 도체를 직접 연결하는 좁은 도체를 사용하십시오. 3. 앞쪽의 "좁은" 도체의 폭은 보드의 정확도 등급과 보드를 통과하는 전류에 따라 선택됩니다.

쌀. 3. 넓은 도체를 접촉 패드에 연결하는 예

2.2.2 SMT 구성 요소의 다리 사이의 모든 점퍼는 외부에 위치해야 합니다.

납땜 영역(그림 4).

쌀. 4. 도체를 미세회로 패드에 연결하는 예

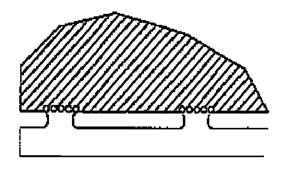

2.2.3 큰 다각형에 위치한 SMD 구성요소의 위치는 다음과 같아야 합니다.

점퍼로 매립지와 분리해야 합니다(“열 접촉” - 그림 5.).

쌀. 5. 대형 폴리곤에 SMT 구성 요소 사이트를 배치한 예

표면 실장 부품의 설치 품질은 비아의 올바른 실행에 크게 좌우됩니다. SMT 부품 패드에 비해 비아를 잘못 배치하는 것은 일반적인 설계 실수입니다.

비아는 부품 패드에 배치하면 안 됩니다. 그림에서. 그림 6은 비아와 패드의 권장 위치를 보여줍니다.

쌀. 6. 경유 위치의 예

2.4.1 보드의 마킹은 실크 스크린 인쇄 또는 도체 층을 사용하여 수행됩니다.

2.4.2 그래픽 및 구성 요소 지정은 보드 구성 요소의 극성과 방향을 반영해야 합니다.

2.4.3 보호 마스크로 덮인 보드 영역에만 실크스크린 인쇄를 사용하여 만든 표시를 배치하는 것이 좋습니다.

2.4.4 서로 인접한 구성요소의 표시 요소는 서로 교차하거나 중첩되어서는 안 됩니다. 마스크에서 열린 영역에 떨어지고 마감 코팅(POS-61, 침지 금 등)으로 덮인 마킹 요소는 적용되지 않는다는 점을 고려해야 합니다.

2.5 인쇄 회로 기판 베이스의 기술 블랭크에 대한 요구 사항.

자동 설치용 보드를 생산에 투입하기 전에 기술 영역(스트립)이 있는 단일 보드 또는 보드 패널 형태의 단일 보드에서 기술 블랭크가 생성됩니다. 공작물 매개변수:

- 권장 공작물 크기 250.0x350.0mm;

- 보드 블랭크 시트의 두께는 0.5...4.2mm입니다.

- 마스크의 흰색과 노란색 색상은 허용되지 않습니다.

- 인쇄 회로 기판 블랭크의 최대 무게는 3kg입니다.

2.6 기술 구역.

기술 구역(그림 7)은 여러 기능을 동시에 수행합니다.

- 구성 요소의 자동 설치를 위해 라인에 공작물을 고정하는 데 사용됩니다.

- 거의 보드 가장자리에 구성 요소를 배치할 수 있습니다.

- 참조 표시를 배치하는 데 사용됩니다.

- 두께가 작고 내부 컷아웃 수가 많은 경우 공작물에 추가 강성을 부여하는 데 사용됩니다.

쌀. 7개 기술 구역.

기술 영역은 일반적으로 공작물의 긴 측면을 따라 위치하며 너비는 5mm입니다. 기술 영역은 스크라이빙이나 브리지를 통해 공작물과 분리됩니다. 기술 영역의 사용이 허용되지 않는 경우 보드에는 구성 요소가 없고 기술 영역의 특성에 맞는 영역이 제공되어야 합니다.

2.7 기준 마크.

레퍼런스 마크는 보드 조립 단계에서 좌표계의 중심입니다. 이를 통해 자동 부품 설치 라인의 장비는 보드에 부품을 자동으로 설치하는 동안 누적되는 전류 좌표 측정 오류를 수정할 수 있습니다.

레퍼런스 마크에는 글로벌(글로벌 기준)과 로컬(로컬 기준)의 두 가지 유형이 있습니다.

1. 글로벌 라벨은 전체 보드에 사용되거나 여러 보드가 패널로 결합된 경우 전체 패널을 묶는 데 사용됩니다. 최소 2개의 글로벌 마크가 필요하며 일반적으로 보드의 대각선 반대쪽 모서리에 가능한 최대 거리를 두고 위치합니다. 전역 레이블은 구성 요소를 포함하는 모든 레이어에 있어야 합니다.

2. 로컬 라벨은 좌표(X,Y 오프셋)를 계산하기 위해 특정 구성 요소(일반적으로 핀 수가 많고 핀 사이에 작은 간격이 있음)를 바인딩하는 데 사용됩니다. 로컬 참조 마크는 일반적으로 특정 구성 요소가 차지하는 영역의 둘레에 대각선으로 위치합니다. 여유 공간이 충분하지 않은 경우 하나의 로컬 참조 마크를 사용하는 것이 허용되며, 가급적이면 구성 요소가 차지하는 영역의 중앙에 사용하십시오.

모든 표시는 도체 및 구성 요소에 대한 금지 영역 외부에 있습니다.

당사 장비의 경우 채워진 원 모양(A = (0.8...3.0)mm)의 참조 표시를 사용하는 것이 좋습니다(그림 8). 레퍼런스 마크의 권장 크기 "A"는 1.0mm입니다.

인쇄 회로 기판(패널)의 참조 표시는 모양과 크기가 동일해야 합니다.

쌀. 8. 적용 가능한 레퍼런스 마크

도체, 구성 요소 및 태그 주변에는 금지된 영역이 있어야 합니다. 보호 마스크. 모든 표시는 도체 레이어에 표시되어야 합니다. 태그는 마스크에서 자유로워야 하며 매끄럽고 빛을 반사하는 금속 코팅(니켈, 주석 합금, 은 등)이 있어야 합니다. 마크와 보드 가장자리 사이의 거리는 최소 5.0mm에 밴드갭 너비를 더한 값이 있어야 합니다. 그림 9와 같이 지점에 표시를 하는 것이 좋습니다.

그림 9 참조 마크 배치의 예.

2.8 공작물에 여러 개의 보드 배치.

필요한 경우 단일 보드를 패널로 결합합니다(그림 10).

쌀. 10 하나의 공작물에 여러 보드를 배열한 예입니다.

보드 사이의 거리는 보드 분리에 사용되는 기술 요구 사항(밀링(그림 11), 윤곽선을 따라 긁기(스크라이빙, 그림 12))을 준수해야 합니다.

쌀. 11. 밀링에 의한 보드 분리의 예

쌀. 12 스크라이빙에 의한 기판 분리의 예.

결함 라인은 한편으로는 솔더 페이스트를 도포하고 부품을 설치할 때 회로 기판이 있는 패널에 충분한 강도를 제공해야 하며, 다른 한편으로는 파손 시 완성된 회로 기판의 분리를 보장해야 합니다.

표면 실장(SMT)

이 기사에는 인쇄 회로 기판에 전자 부품을 표면 실장하는 기술에 대한 설명이 포함되어 있습니다. 일반적인 용어가 제공되고 표면 실장 프로세스에 대한 설명이 제공됩니다. 이 기술을 사용할 때의 주요 장점과 단점이 표시됩니다. 또한 이 기술 프로세스를 구현하는 데 필요한 장비 목록이 제공됩니다.

용어 및 정의

이 기사에서는 일반적으로 인정되는 여러 용어를 사용하며, 우리가 이해한 바에 따라 해당 용어를 제시하고 정의할 것입니다.

표면 실장 - 생산 기술, 전자 부품 설계, 모듈, 인쇄 회로 기판 제품. 또한 "표면 실장"이라는 문구는 때때로 이 용어의 동의어로 사용됩니다.

SMT - 표면 실장 기술. 이 용어와 약어는 위에 주어진 용어와 유사하게 국내외 문헌 모두에서 표면 실장 기술을 나타내는 데 사용됩니다.

칩 부품 - 표면 실장 기술을 사용하여 인쇄 회로 기판에 실장된 전자 부품입니다.

SMD - 표면 장착 장치. 이 약어와 용어는 국내외 문헌에서 칩 부품을 지칭하는 데 사용됩니다.

인쇄 회로 기판 - 하나 이상의 전기 회로를 포함하는 유전체 재료로 만들어진 판(보통 직사각형 모양)입니다. 전기 회로는 스탬핑이나 인쇄로 형성됩니다.

솔더 페이스트

- 플럭스를 함유하고 땜납과 다수의 유기 충전재로 구성된 분말 형태의 혼합물입니다. 솔더 페이스트라는 용어는 때때로 이 용어의 동의어로 사용됩니다.

표면 실장 공정

표면 실장 공정을 보장하기 위해 여러 주요 단계가 수행되며 그 중 다음 사항이 먼저 강조 표시되어야 합니다.

인쇄 회로 기판 디자인. 이 단계에서는 전기 회로 설계, 접촉 패드, 원하는 위치에 맞는 칩 부품 선택, 인쇄 회로 기판 유전체 선택 등이 이루어집니다. 인쇄회로기판 제조. 인쇄 회로 기판의 설계에 따라 인쇄 회로 기판의 생산은 스탬핑 또는 인쇄로 수행됩니다.

인쇄 회로 기판에 솔더 페이스트를 적용합니다. 솔더 페이스트는 칩 부품의 고정제 역할을 합니다. 칩 부품 설치. 칩 부품은 접촉 패드에 설치되고 솔더 페이스트로 고정됩니다. 인쇄 회로 기판을 납땜합니다. 표면 실장 기술의 이 단계는 특수 용해로에서 솔더 페이스트의 그룹 리플로우를 통해 수행됩니다.

위 단계 중 마지막 세 단계는 표면 실장 기술과 직접적으로 관련됩니다. 즉, 솔더 페이스트 적용, 칩 구성 요소 설치 및 그룹 방법을 사용한 솔더 페이스트 솔더링입니다. 좀 더 자세히 살펴보겠습니다.

솔더 페이스트 도포

표면 실장 기술의 솔더 페이스트는 매우 중요한 구성 요소이며, 적용 절차 자체와 구현 품질이 최종 전자 제품의 품질에 큰 영향을 미칩니다.

솔더 페이스트는 칩 부품용 솔더 기능을 수행할 뿐만 아니라 솔더가 녹을 때까지 접촉 패드에 칩 부품을 고정하는 보조 기능도 수행합니다. 그렇기 때문에 무엇보다도 솔더 페이스트를 선택할 때 접착 특성을 평가해야 합니다.

솔더 페이스트를 올바르게 도포하기 위해 스크린 프린터가 사용됩니다. 스크린 프린터는 수동 또는 자동일 수 있습니다. 스크린 프린터의 선택은 주로 작동 조건과 제조된 전자 제품의 생산량에 따라 결정됩니다. 어떤 경우든 사용되는 스크린 프린터에 관계없이 솔더 페이스트를 적용할 방법과 양은 공정 엔지니어가 결정합니다.

따라서 표면 실장 공정에서 솔더 페이스트 도포 단계가 중요한 역할을 한다는 점에 유의해야 합니다. 이 단계에서 발생한 오류는 이후 제조된 전자 제품의 결함 및 결함으로 이어질 수 있습니다.

칩 부품 설치.

칩 구성 요소를 설치하는 것은 대체로 기계적 절차입니다. 주요 임무는 인쇄 회로 기판에 칩 구성 요소를 올바르게 배치하는 것입니다. 모든 SMD 구성요소는 설계에 따라 엄격하게 설치되어야 합니다. 전자 회로제조 인쇄 회로 기판. 배치 오류가 발생하는 경우 결과 제품은 기껏해야 작동하지 않으며 최악의 경우 단락 및 화재가 발생할 수 있음이 분명합니다.

이 단계에서 인적 요소를 제거하기 위해 로봇 또는 자동화된 프로그래밍 가능 설치 프로그램이 가장 자주 사용되어 잘못된 설치의 위험을 줄입니다.

인쇄 회로 기판을 납땜합니다.

솔더 페이스트가 PCB에 적용되고 SMD 구성 요소가 설치 및 고정되면 솔더 페이스트 리플로우 단계가 수행됩니다. 인쇄 회로 기판의 솔더를 리플로우할 때 온도 체계 및/또는 온도 프로파일을 유지하는 것이 매우 중요합니다. 온도 체계는 최대 가열 온도뿐만 아니라 이 온도가 어떻게 달성되는지에 따라 특징이 있습니다. 가열 과정에서 다수의 칩 구성 요소가 지정된 가열 속도를 유지해야 합니다. 즉, 리플로우 동안 리플로우 온도와 온도에 도달해야 하는 시간이 설정됩니다. 더욱이 냉각 절차도 이러한 상황을 견뎌야 합니다. 이러한 접근 방식은 인쇄 회로 기판과 그 위에 있는 SMD 구성 요소가 열 충격을 받지 않도록 하여 열 손상으로부터 보호하는 데 도움이 됩니다.

지정된 것을 보장하려면 온도 체계리플로우에는 소위 솔더 리플로우 오븐이 사용됩니다. 솔더 리플로우 오븐을 사용하면 인쇄 회로 기판의 칩 구성 요소 그룹 솔더링에 대한 온도 프로필 요구 사항을 충족할 수 있습니다. 솔더 리플로우 오븐은 사용하는 가열 방법이 다양하며 각각 고유한 장점과 단점이 있습니다. 현재 가장 일반적인 방법 중에는 대류 방법이 있습니다. 물론 특정 퍼니스의 선택은 주로 제조되는 제품의 온도 프로파일과 성능에 따라 달라집니다.

솔더 리플로우 절차와 실행 품질은 결과적으로 인쇄 회로 기판의 품질을 결정하고 의심할 여지 없이 이 기판이 설치될 전자 제품의 품질을 결정합니다.

표면 실장 기술의 장점과 단점.

표면 장착의 주요 장점 중에서 중요한 순서대로 다음 사항을 언급해야 합니다.

직렬 전자 제품의 비용이 크게 절감됩니다.

전자 제품을 구성하는 데 사용되는 칩 구성 요소와 회로의 통합 및 표준화.

프로세스 자동화 기능이 향상되었습니다.

더 나은 수리 가능성.

칩 구성 요소의 크기를 줄이고 결과적으로 비용을 절감합니다.

칩 부품의 크기를 줄여 전자제품의 무게를 줄입니다.

표면 장착의 단점은 다음과 같습니다.

솔더 페이스트 적용 기술, 솔더 페이스트 용융 중 온도 프로파일 등을 엄격하게 따라야합니다.

첫 번째 사항으로 인해 사용되는 기술 장비에 대한 요구 사항이 높습니다.

두 번째 결과는 생산 라인 장비에 대한 상당한 초기 비용입니다.

전자 칩 부품의 보관 및 운송에 대한 요구 사항이 증가했습니다.

결론.

표면 실장을 사용하면 비용을 유지하고 심지어 절감하면서 전자 제품의 생산량을 크게 늘릴 수 있습니다. 이는 광범위한 자동화, SMD 부품의 크기 감소, 프로세스 통합 및 노동 강도 감소를 통해 달성됩니다. 존재하는 모든 단점에도 불구하고 결과적인 효과는 의심할 여지 없이 이 기술의 약속과 요구를 말해줍니다.

인쇄회로기판에 적용되는 표시도 디자인 요소입니다. 마킹의 목적과 실행 기술(기술)은 각 특정 사례에 따라 결정되는 여러 요소에 따라 달라집니다. 라벨링 매개변수는 GOST 2.314-68의 요구 사항을 충족해야 합니다. 이는 설계 문서에 표시되어 있으며 컴퓨터 미디어(자기 미디어, 플로피 디스크)의 데이터 형식으로 기술 프로젝트의 일부입니다.

의도 된 목적에 따라 마킹은 기본 및 추가 (보조)가 될 수 있으며 첫 번째는 반드시 인쇄 회로 기판에 적용됩니다.

주요 표시에는 인쇄 회로 기판 또는 해당 코드의 지정, 제조 날짜 및 포토마스크(프로젝트) 버전의 일련 번호가 포함됩니다. 주요 표시에는 보드 외곽선 외부(기술 분야) 포토마스크에 생성된 일부 기호 및 기호가 포함되며, 이 정보는 각 레이어에 적용되며 인쇄 회로 기판 제조업체가 프로젝트에 가장 자주 도입합니다.

추가 표시에는 보드(또는 배치)의 일련 번호 또는 일련 번호, 요소의 위치 지정, 요소의 설치(설치) 위치에 대한 그래픽 표현, 번호 매기기 또는 상징개발자의 재량에 따라 첫 번째 결론, 극성 요소 및 기타 정보에 대한 더하기 기호.

마킹의 일부(또는 전체)는 인쇄 전도체 기술(일반적으로 에칭)을 사용하여 구현할 수 있습니다. 그러나 도체와 함께 보드 표면에 적용되며 때로는 결합하기가 어렵습니다. 따라서 이 방법은 필수 표시에만 사용됩니다. 추가 마킹은 정확도 등급이 낮은 인쇄 회로 기판(1차 및 2차, 드물게 3차)에 에칭을 수행한 다음 여유 공간이 있는 경우에만 수행됩니다.

일반적으로 에칭을 통해 보드의 지정과 포토마스크의 버전 번호(문자)가 수행됩니다. 치수(또는 여유 공간)로 인해 보드 지정을 완전히 입력할 수 없는 경우(15자 초과) 마지막 세 자리로 줄이거나 코드가 입력됩니다. 디자인이나 동봉된 문서에 명시되어 있습니다. 이러한 마킹의 필요성은 대량 생산 시 각 보드를 식별해야 하기 때문에 발생합니다. 대량 생산에서는 많은 수의 보드와 그 조각(MPP의 내부 레이어)이 동시에 생산될 수 있습니다.

에칭을 사용하면 더하기 기호가 극성 요소에 배치되고 설치 중에 모호한 설치를 허용하는 요소의 첫 번째 터미널 지정이 종종 배치됩니다.

현대 기술을 사용하면 모든 유형의 표시에 대해 단단한 표면에 페인트와 인쇄를 사용할 수 있습니다. 이는 일반적으로 오프셋 인쇄 방법이라고 합니다.

제품에 마킹을 하려면 프로젝트에서 모든 마킹 정보를 포함하는 하나 또는 두 개의 독립적인 레이어를 개발해야 합니다. 주요 요구 사항은 표시가 납땜 영역에 들어가는 것을 방지하는 것입니다. 보호용 마스크가 있는 경우 이 조건은 쉽게 충족됩니다. 모든 표시는 보호층 내에 있어야 합니다.

표시의 경우 표준 글꼴(GOST 26.020-80)과 스타일이 가까운 글꼴을 선택해야 합니다. 실제로 이는 초기 프로그램 구성(템플릿에서) 및 텍스트 스타일 대화상자 중에 설치된 글꼴 중 하나일 수 있습니다.

글꼴의 크기(높이)는 디자이너가 설정하며 마킹 기술에 따라 다릅니다. 에칭으로 얻은 비문의 높이는 2.5mm 이상이어야 합니다. 그렇지 않으면 글꼴을 읽을 수 없습니다. 때때로 비문은 우편 봉투의 색인에 사용되는 양식화된 우편 글꼴로 표시됩니다. 이 경우 텍스트(주로 숫자)는 선분(실제로는 인쇄된 도체)으로 구성되며 그 너비는 인쇄 회로 기판의 정확도 등급에 따라 달라집니다(글꼴 높이는 너비보다 15배 커야 함). 라인).

오프셋 인쇄 방법을 사용하여 만든 비문의 경우 글꼴 높이는 최소 1.5mm 이상이어야 합니다.

동일한 방법을 사용하여 인쇄 회로 기판의 영역 분할 선, 구성 요소 설치 위치, 일반 및 극성 요소의 기존 이미지와 같은 그래픽 정보를 보드에 적용할 수 있습니다. 별도로 부착 지점 등에 주목할 가치가 있습니다. 이 경우 사실상 제한이 없습니다. 그래픽 요소의 최소 선 너비는 0.1mm이며 비문 제조 기술에 따라 크게 결정됩니다.

페인트 마킹의 색상은 배경(기판)의 색조에 따라 디자이너가 설정합니다. 대부분의 경우 흰색 페인트가 선호됩니다. 페인트를 선택할 때 중성 용제(알코올, 프레온, 톨루엔, 가솔린) 또는 이들의 혼합물에 대한 내성을 고려해야 합니다. 이 목적에 적합한 페인트는 PF-115, EP-572 및 기타 일부, 특히 Coats(영국)의 흰색 페인트 AQXZ500T입니다.

인쇄 회로 기판의 요소 표시 예가 그림 1에 나와 있습니다. 1.22.

그룹 방식으로 인쇄회로기판에 마킹하는 것 외에도 스탬프나 드로잉 펜을 사용하여 수동으로 마킹할 수 있습니다. 글꼴이 GOST 2.008-85를 준수하고 높이가 3mm 이상이며 필요한 지침이 설계 문서에 포함되어 있는지 확인해야 합니다. TNPF-58 페인트(또는 유사한 페인트)를 사용하여 스탬프로 적용한 비문은 기후 영향에 대한 저항력이 충분하지 않으므로 일반적으로 UR-231과 같은 투명한 바니시로 덮여 있습니다. 동일한 마킹이지만 PF-115 또는 EP-572 페인트로 만들어지면 바니싱이 필요하지 않습니다. 그림에서. 그림 1.23은 다양한 표시 옵션이 있는 인쇄 회로 기판의 일부를 보여줍니다.

Rav, Rabbi, Rebbe - 그는 누구입니까?

Rav, Rabbi, Rebbe - 그는 누구입니까? 아벨라르의 철학 - 개념주의

아벨라르의 철학 - 개념주의 큰 자개 또는 큰 숲 자개 나비 자개는 어떻게 생겼습니까?

큰 자개 또는 큰 숲 자개 나비 자개는 어떻게 생겼습니까?